# ELECTRÓNICA DIGITAL

Sistemas de Numeración, Lógica Combinacional y Secuencial

Irene Tustón, Christiam Núñez,

Mónica Carrión & Luis Sánchez

EDITORIAL

**SAGA**

# **Electrónica Digital**

## **Sistemas de Numeración, Lógica**

## **Combinacional y Secuencial**

### **Autores:**

*Irene Tustón Torres*

*Christiam Xavier Núñez Zavala*

*Mónica Alexandra Carrión Cevallos*

*Luis Miguel Sánchez Muyulema*

## Datos bibliográficos

**ISBN:** 978-9907-803-03-7

**Título del libro:** Electrónica Digital

Sistemas de Numeración, Lógica Combinacional y Secuencial

**Autores:** Tustón Torres, Irene

Núñez Zavala, Christiam Xavier

Carrión Cevallos, Mónica Alexandra

Sánchez Muyulema, Luis Miguel

**Editorial:** SAGA

**Materia:** 621.38 - Electrónica. Ingeniería de las comunicaciones

**Público objetivo:** Profesional / académico

**Publicado:** 2026-01-27

**Número de

edición:** 1

**Tamaño:** 5Mb

**Soporte:** Libro digital descargable

**Formato:** Pdf (.pdf)

**Idioma:** Español

**DOI:** <https://doi.org/10.63415/saga.2026.59>

Hecho en Ecuador / Made in Ecuador

## Sinopsis

*Electrónica Digital: Sistemas de Numeración, Lógica Combinacional y Secuencial* presenta una visión integral de los principios que sustentan el diseño y análisis de sistemas digitales contemporáneos, articulando fundamentos matemáticos, representación de la información y técnicas de implementación con rigor didáctico. El texto aborda los sistemas de numeración y sus conversiones con claridad operativa, integra la aritmética binaria y los complementos como herramientas formales, y desarrolla los códigos digitales empleados en la comunicación y el procesamiento de datos. La obra avanza hacia el álgebra de Boole, las funciones lógicas, las tablas de verdad y los métodos de simplificación, vinculándolos con compuertas y familias lógicas para una comprensión funcional del hardware. Posteriormente, el análisis combinacional se construye mediante sumadores, comparadores, codificadores, decodificadores, multiplexores y demultiplexores, fortaleciendo el razonamiento estructurado mediante ejemplos y actividades. El estudio de la lógica secuencial consolida señales de reloj, multivibradores, celdas binarias, flip-flops, diagramas de estado y máquinas secuenciales, con énfasis en sincronismo y comportamiento temporal. La propuesta didáctica combina teoría, práctica y autoevaluación, favoreciendo la aplicación en automatización, control y telecomunicaciones. Su enfoque progresivo y sistemático apoya la formación técnica y universitaria, promueve precisión conceptual y fomenta competencias para el diseño eficiente de soluciones digitales confiables.

**Palabras clave:** electrónica digital; sistemas de numeración; lógica combinacional; lógica secuencial; álgebra de boole; circuitos digitales

## Synopsis

*Digital Electronics: Number Systems, Combinational and Sequential Logic* offers a comprehensive view of the principles that underpin modern digital system design and analysis, integrating mathematical foundations, data representation, and implementation techniques with strong pedagogical rigor. The book addresses number systems and conversions with operational clarity, develops binary arithmetic and complements as formal tools, and presents digital codes used for communication and data processing. It then advances to Boolean algebra, logical functions, truth tables, and simplification methods, connecting them with logic gates and logic families for a functional understanding of hardware. Combinational analysis is built through adders, comparators, encoders, decoders, multiplexers, and demultiplexers, strengthening structured reasoning through examples and guided activities. The treatment of sequential logic consolidates clock signals, multivibrators, binary cells, flip-flops, state diagrams, and sequential machines, emphasizing synchronism and temporal behavior. The didactic proposal blends theory, practice, and self-assessment, supporting applications in automation, control, and telecommunications. Its progressive and systematic approach supports technical and higher education, promotes conceptual precision, and fosters competencies for the efficient design of reliable digital solutions.

**Keywords:** digital electronics; number systems; combinational logic; sequential logic; boolean algebra; digital circuits

El contenido y las ideas expuestas en esta obra se encuentran protegidos por la normativa vigente en materia de propiedad intelectual y constituyen derechos exclusivos de su(s) autor(es)

Todos los derechos reservados © 2026

## Contenido

|                                                 |           |

|-------------------------------------------------|-----------|

| <b>PRESENTACIÓN-ENMARCACIÓN .....</b>           | <b>11</b> |

| A. AUTORES .....                                | 11        |

| B. INTRODUCCIÓN .....                           | 15        |

| DESCRIPCIÓN .....                               | 15        |

| COMPETENCIAS.....                               | 15        |

| OBJETIVOS DE LA ASIGNATURA .....                | 15        |

| <br>                                            |           |

| <b>UNIDAD 1: SISTEMAS DE NUMERACIÓN .....</b>   | <b>17</b> |

| 1.1 CONVERSIONES .....                          | 17        |

| 1.1.1 CONVERSIÓN DE DECIMAL A BINARIO .....     | 17        |

| 1.1.2 CONVERSIÓN DE BINARIO A DECIMAL.....      | 18        |

| 1.1.3 CONVERSIÓN DE DECIMAL A HEXADECIMAL ..... | 19        |

| 1.1.4 CONVERSIÓN DE HEXADECIMAL A DECIMAL ..... | 19        |

| 1.1.5 CONVERSIÓN DE BINARIO A HEXADECIMAL.....  | 20        |

| 1.1.6 CONVERSIÓN DE HEXADECIMAL A BINARIO.....  | 20        |

| 1.2 ARITMÉTICA BINARIA.....                     | 21        |

| 1.2.1 SUMA BINARIA.....                         | 21        |

| 1.2.2 RESTA BINARIA .....                       | 22        |

| 1.2.3 MULTIPLICACIÓN BINARIA.....               | 24        |

| 1.2.4 DIVISIÓN BINARIA .....                    | 25        |

| 1.3 COMPLEMENTOS .....                          | 25        |

| 1.3.1 COMPLEMENTO A 1 .....                     | 25        |

| 1.3.2 COMPLEMENTO A 2 .....                     | 26        |

| 1.4 CÓDIGOS .....                               | 27        |

| 1.4.1 CÓDIGO DECIMAL BINARIO (BCD).....         | 27        |

|                                                                                       |                  |

|---------------------------------------------------------------------------------------|------------------|

| 1.4.1.1 CÓDIGO 8421.....                                                              | 27               |

| 1.4.2 CÓDIGOS DECIMALES .....                                                         | 29               |

| 1.4.2.1 CÓDIGO GRAY.....                                                              | 29               |

| 1.4.2.2 CÓDIGOS ALFANUMÉRICOS .....                                                   | 31               |

| 1.4.2.2.1 CÓDIGO ASCII .....                                                          | 32               |

| <b><u>ACTIVIDADES.....</u></b>                                                        | <b><u>36</u></b> |

| ACTIVIDAD 1: EJERCICIOS SOBRE CONVERSIÓNES.....                                       | 36               |

| ACTIVIDAD 2: EJERCICIOS SOBRE ARITMÉTICA BINARIA. ....                                | 36               |

| ACTIVIDAD 3: EJERCICIOS SOBRE COMPLEMENTOS. ....                                      | 36               |

| ACTIVIDAD 4: EJERCICIOS SOBRE CÓDIGOS.....                                            | 37               |

| ACTIVIDAD 5: AUTOEVALUACIÓN.....                                                      | 37               |

| <b>UNIDAD 2: ÁLGEBRA DE BOOLE Y FUNCIONES.....</b>                                    | <b>39</b>        |

| 2.1 ÁLGEBRA DE BOOLE, OPERACIONES, TEOREMAS, POSTULADOS, LEYES Y PROPIEDADES .....    | 39               |

| 2.1.1 ÁLGEBRA DE BOOLE .....                                                          | 39               |

| 2.1.2 FUNCIÓN LÓGICA .....                                                            | 40               |

| 2.1.3 TABLA DE VERDAD .....                                                           | 41               |

| 2.2 FORMAS CANÓNICAS DE UNA FUNCIÓN LÓGICA BOOLEANA .....                             | 43               |

| 2.2.1 PRIMERA FORMA CANÓNICA.....                                                     | 43               |

| 2.2.2 SEGUNDA FORMA CANÓNICA .....                                                    | 44               |

| 2.3 SIMPLIFICACIÓN DE ECUACIONES BOOLEANAS: MÉTODO ALGEBRAICO, MAPAS DE KARNAUGH..... | 45               |

| 2.3.1 MÉTODO ALGEBRAICO PARA SIMPLIFICACIÓN DE FUNCIONES.....                         | 46               |

| 2.3.2 MÉTODO DE KARNAUGH PARA SIMPLIFICACIÓN DE FUNCIONES.....                        | 47               |

| 2.4 COMPUERTAS LÓGICAS, DISEÑO E IMPLEMENTACIÓN DE FUNCIONES .....                    | 50               |

| 2.4.1 CIRCUITOS INTEGRADOS DIGITALES COMERCIALES .....                                | 52               |

| 2.5 FAMILIAS LÓGICAS E INTERFACES .....                                               | 53               |

| 2.5.1 FAMILIA LÓGICA TTL.....                                                         | 54               |

| 2.5.2 FAMILIA LÓGICA CMOS .....                                                       | 55               |

|                                                                                      |           |

|--------------------------------------------------------------------------------------|-----------|

| 2.5.3 COMPATIBILIDAD ENTRE LAS FAMILIAS LÓGICA TTL Y CMOS.....                       | 56        |

| <b><u>ACTIVIDADES</u></b> .....                                                      | <b>58</b> |

| <b>ACTIVIDAD 1: EJERCICIOS SOBRE TABLA DE VERDAD.</b> .....                          | 58        |

| <b>ACTIVIDAD 2: EJERCICIOS SOBRE FORMAS CANÓNICAS.</b> .....                         | 58        |

| <b>ACTIVIDAD 3: EJERCICIOS SOBRE SIMPLIFICACIÓN DE ECUACIONES BOOLEANAS.</b> .....   | 58        |

| <b>ACTIVIDAD 4: AUTOEVALUACIÓN.</b> .....                                            | 59        |

| <br>                                                                                 |           |

| <b>UNIDAD 3: ANÁLISIS LÓGICO COMBINACIONAL .....</b>                                 | <b>61</b> |

| <b>3.1 SUMADORES, RESTADORES, MULTIPLICADORES, COMPARADORES .....</b>                | <b>61</b> |

| <b>3.1.1 SUMADORES.....</b>                                                          | <b>61</b> |

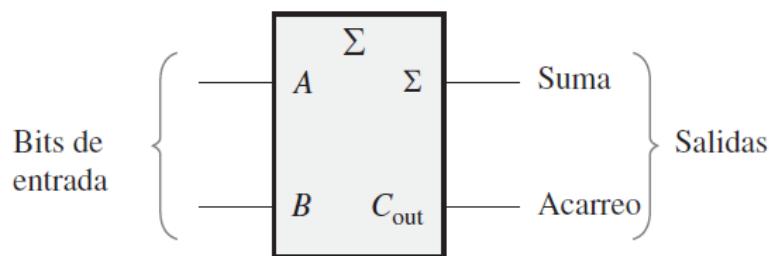

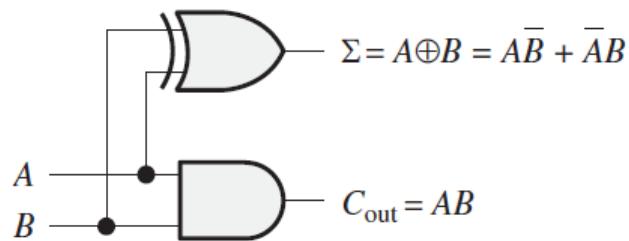

| <b>3.1.1.1 SUMADORES BÁSICOS.....</b>                                                | <b>61</b> |

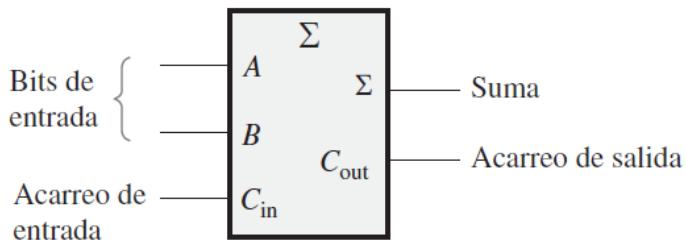

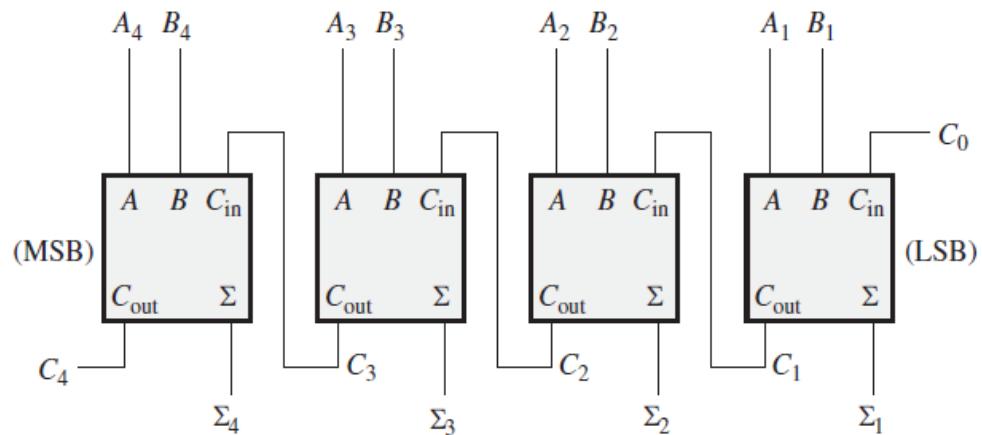

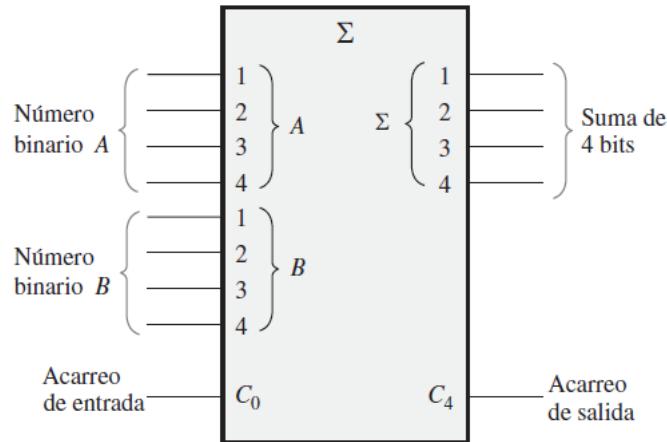

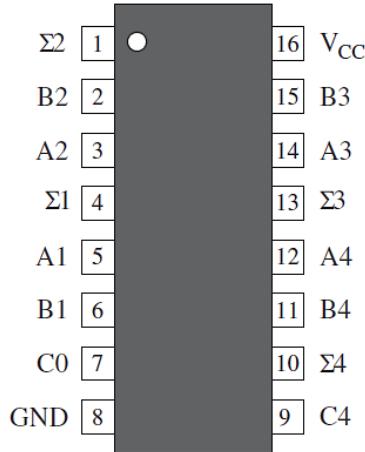

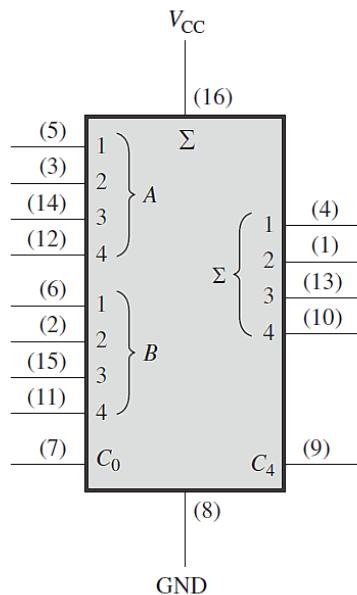

| <b>3.1.1.2 SUMADORES COMPLETOS.....</b>                                              | <b>63</b> |

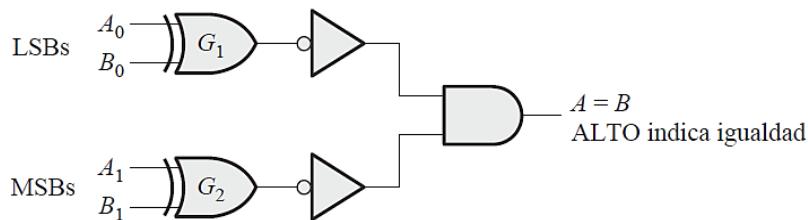

| <b>3.1.2 COMPARADORES .....</b>                                                      | <b>71</b> |

| <b>3.1.2.1 IGUALDAD.....</b>                                                         | <b>71</b> |

| <b>3.1.2.2 DESIGUALDAD .....</b>                                                     | <b>73</b> |

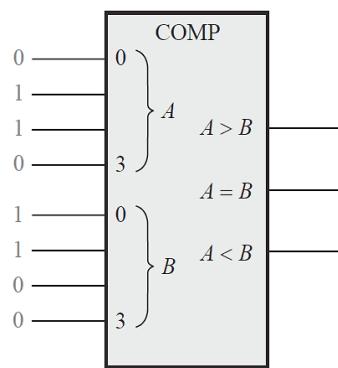

| <b>3.1.2.3 COMPARADOR DE MAGNITUD DE 4 BITS 74HC85.....</b>                          | <b>74</b> |

| <b>3.2 DECODIFICADORES .....</b>                                                     | <b>75</b> |

| <b>3.2.1 DECODIFICADOR BINARIO BÁSICO .....</b>                                      | <b>75</b> |

| <b>3.2.2 DECODIFICADOR DE 4 BITS .....</b>                                           | <b>76</b> |

| <b>3.2.3 DECODIFICADOR BCD A DECIMAL.....</b>                                        | <b>80</b> |

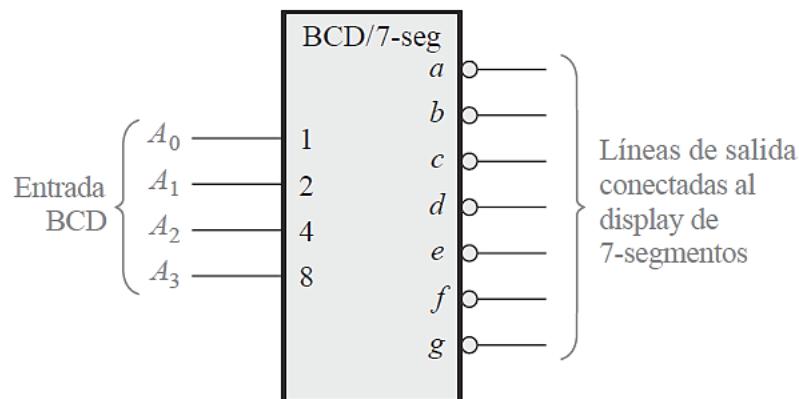

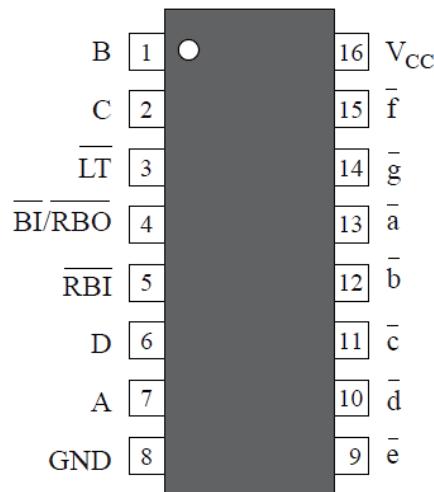

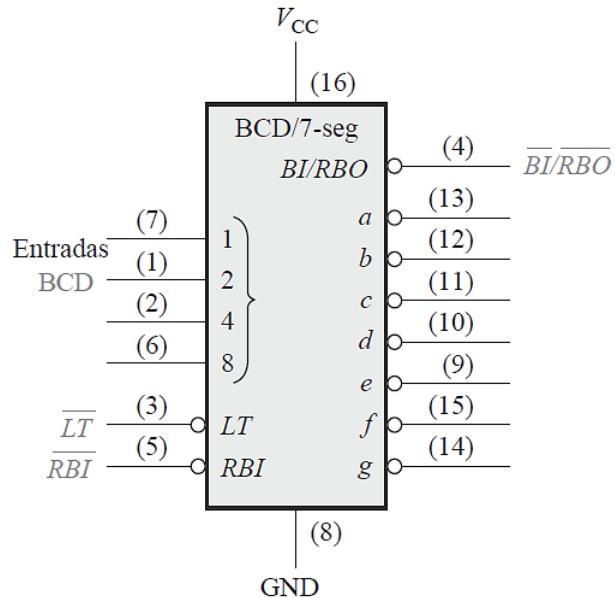

| <b>3.2.4 DECODIFICADOR BCD A 7 SEGMENTOS .....</b>                                   | <b>81</b> |

| <b>3.3 CODIFICADORES.....</b>                                                        | <b>83</b> |

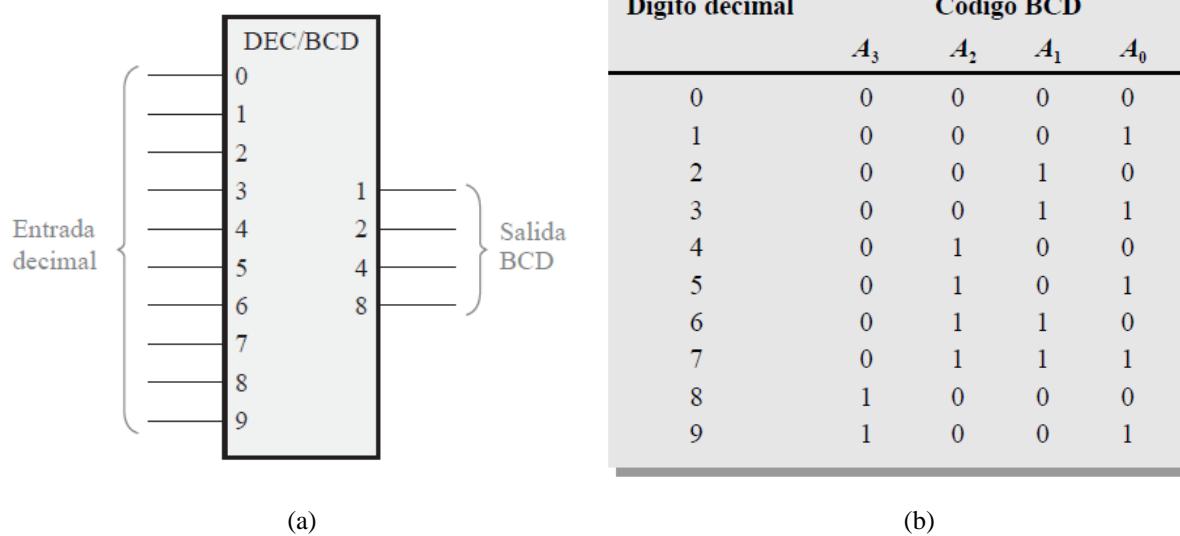

| <b>3.3.1 CODIFICADOR DECIMAL A BCD .....</b>                                         | <b>83</b> |

| <b>3.4 MULTIPLEXORES Y DEMULTIPLEXORES .....</b>                                     | <b>86</b> |

| <b>3.4.1 MULTIPLEXORES.....</b>                                                      | <b>86</b> |

| <b>3.4.1.1 CUÁDRUPLE MULTIPLEXOR / SELECTOR DE DATOS DE 2 ENTRADAS 74HC157 .....</b> | <b>88</b> |

| <b>3.4.1.2 MULTIPLEXOR / SELECTOR DE DATOS DE 8 ENTRADAS 74LS151.....</b>            | <b>89</b> |

| <b>3.4.2 DEMULTIPLEXORES.....</b>                                                    | <b>90</b> |

|                                                                                  |            |

|----------------------------------------------------------------------------------|------------|

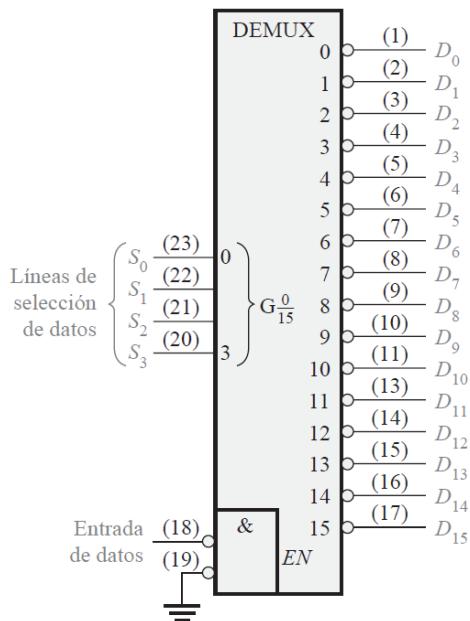

| 3.4.2.1 DEMULTIPLEXOR 74HC154 .....                                              | 91         |

| <b><u>ACTIVIDADES</u></b> .....                                                  | <b>92</b>  |

| ACTIVIDAD 1: CUESTIONARIO SOBRE SUMADORES .....                                  | 92         |

| ACTIVIDAD 2: CUESTIONARIO SOBRE COMPARADORES.....                                | 92         |

| ACTIVIDAD 3: CUESTIONARIO SOBRE DECODIFICADORES.....                             | 92         |

| ACTIVIDAD 4: CUESTIONARIO SOBRE CODIFICADORES.....                               | 92         |

| ACTIVIDAD 5: CUESTIONARIO SOBRE MULTIPLEXORES Y DEMULTIPLEXORES.....             | 92         |

| ACTIVIDAD 6: AUTOEVALUACIÓN.....                                                 | 93         |

| <br>                                                                             |            |

| <b>UNIDAD 4: ANÁLISIS LÓGICO SECUENCIAL.....</b>                                 | <b>95</b>  |

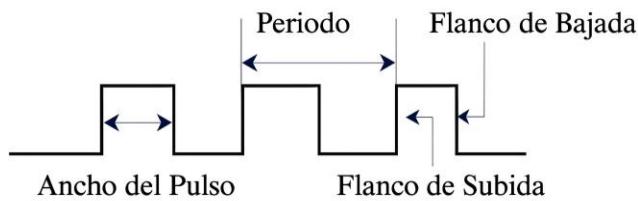

| 4.1 SEÑALES DE RELOJ Y MULTIVIBRADORES .....                                     | 95         |

| 4.1.1 MULTIVIBRADOR MONOESTABLE.....                                             | 96         |

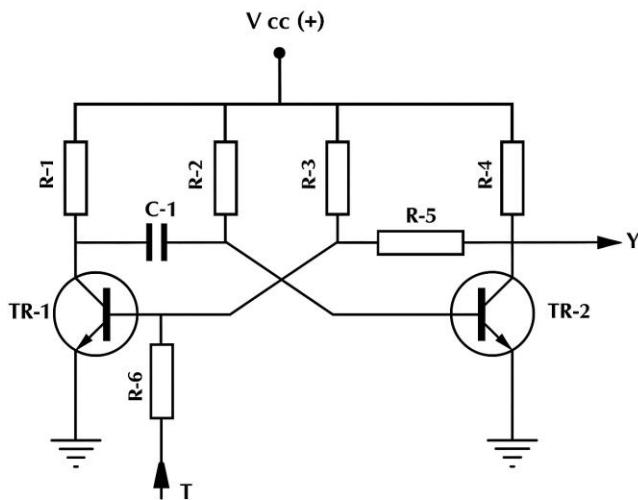

| 4.1.2 MULTIVIBRADOR ASTABLE.....                                                 | 97         |

| 4.1.3 MULTIVIBRADOR BIESTABLE.....                                               | 99         |

| 4.2 LÓGICA SECUENCIAL SINCRONISMO .....                                          | 107        |

| 4.3 CELDAS BINARIAS, FLIP/FLOPS .....                                            | 107        |

| 4.4 DIAGRAMA DE ESTADOS.....                                                     | 117        |

| 4.5 MÁQUINAS SECUENCIALES .....                                                  | 118        |

| <b><u>ACTIVIDADES</u></b> .....                                                  | <b>120</b> |

| ACTIVIDAD 1: CUESTIONARIO SOBRE SEÑALES DE RELOJ Y MULTIVIBRADORES.....          | 120        |

| ACTIVIDAD 2: CUESTIONARIO SOBRE LÓGICA SECUENCIAL SINCRONISMO.....               | 120        |

| ACTIVIDAD 3: CUESTIONARIO SOBRE CELDAS BINARIAS FLIP/FLOPS .....                 | 120        |

| ACTIVIDAD 4: CUESTIONARIO SOBRE DIAGRAMAS DE ESTADO Y MÁQUINAS SECUENCIALES..... | 120        |

| ACTIVIDAD 5: AUTOEVALUACIÓN.....                                                 | 120        |

| <br>                                                                             |            |

| <b><u>BIBLIOGRAFÍA</u></b> .....                                                 | <b>123</b> |

| BIBLIOGRAFÍA BÁSICA .....                                                        | 123        |

| BIBLIOGRAFÍA COMPLEMENTARIA.....                                                 | 123        |

## PRESENTACIÓN-ENMARCACIÓN

### A. AUTORES

|                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Datos Autor                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Nombres y apellidos                                               | Irene Tustón Torres                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Título de tercer nivel<br>(información registrada en la SENESCYT) | Ingeniero en Electrónica, Telecomunicaciones y Redes                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Título de cuarto nivel<br>(información registrada en la SENESCYT) | Magister en Sistemas de Telecomunicaciones                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ORCID:                                                            | <a href="https://orcid.org/0009-0009-3949-534X">https://orcid.org/0009-0009-3949-534X</a>                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Correo electrónico                                                | <a href="mailto:itustn@byupathway.edu">itustn@byupathway.edu</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Resumen hoja de vida                                              | Ingeniera en Electrónica Telecomunicaciones y Redes y Magister en Sistemas de Telecomunicaciones. Actualmente estudiante del Bachelor in Family History en Brigham Young University. Experiencia profesional como técnico computacional en Self Reliant Institute. Experiencia docente en la Escuela Superior Politécnica de Chimborazo, Universidad Nacional de Chimborazo e Instituto Superior Tecnológico Carlos Cisneros. Participación en proyectos de planificación institucional, vinculación e investigación. |

|                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Datos Autor                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Nombres y apellidos                                            | Christiam Xavier Núñez Zavala                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Título de tercer nivel (información registrada en la SENESCYT) | Ingeniero en Electrónica, Control y Redes Industriales                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Título de cuarto nivel (información registrada en la SENESCYT) | Magíster en Sistemas de Control y Automatización Industrial.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ORCID:                                                         | <a href="https://orcid.org/0000-0001-8162-5616">https://orcid.org/0000-0001-8162-5616</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Correo electrónico                                             | <a href="mailto:cnunez@unach.edu.ec">cnunez@unach.edu.ec</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Resumen hoja de vida                                           | <p>Ingeniero en Electrónica, Control y Redes Industriales de la Escuela superior Politécnica de Chimborazo en el año de 2011, Magister en Sistemas de Control y Automatización Industrial en la Superior Politécnica de Chimborazo año de 2017. Jefe de Automatización en la empresa Ecuatoriana de Cerámica planta Azulejos de la Ciudad de Riobamba. Encargado de soporte de líneas de comunicación Grupo Cerámico. Docente de la Escuela Superior Politécnica de Chimborazo en el año 2012 en la Facultad de Informática y Electrónica en las carreras de: Ingeniería Electrónica en Control y Redes Industrial, Ingeniería Electrónica en Telecomunicaciones. Docente en la Universidad Nacional de Chimborazo en la Unidad de Admisión y Nivelación en el año 2017. Analista del departamento de Tecnologías de la Información y Comunicación de la Universidad nacional de Chimborazo. Docente de la Senescyt en el Instituto Tecnológico Carlos Cisneros de la Ciudad de Riobamba en el año 2018. Actualmente Docente de la Universidad Nacional de Chimborazo en la Facultad de Ciencias de la Educación Humanas y Tecnologías, Carrera de Pedagogía de la Informática. Miembro del grupo de Investigación Umayuk de la Universidad nacional de Chimborazo.</p> |

|                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Datos Autor                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Nombres y apellidos                                            | Mónica Alexandra Carrión Cevallos                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Título de tercer nivel (información registrada en la SENESCYT) | Ingeniera de Mantenimiento                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Título de cuarto nivel (información registrada en la SENESCYT) | Magister en seguridad industrial, mención salud ocupacional<br>Magister en matemática aplicada, mención matemática computacional                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ORCID:                                                         | <a href="https://orcid.org/0000-0003-0928-1307?lang=es">https://orcid.org/0000-0003-0928-1307?lang=es</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Correo electrónico                                             | <a href="mailto:moncacevallos@yahoo.es">moncacevallos@yahoo.es</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Resumen hoja de vida                                           | Ingeniera en Mantenimiento, Magíster en Seguridad Industrial y Magíster en Matemática Aplicada, con más de 15 años de experiencia como docente universitaria en la Escuela Superior Politécnica de Chimborazo (ESPOCH) y en el Instituto Superior Universitario Carlos Cisneros, desempeñándome en docencia técnica y en las áreas de Matemática e Investigación; he participado activamente en proyectos de investigación, presentando ponencias internacionales en Argentina y Perú, y publicado cuatro artículos científicos en revistas indexadas, consolidando un perfil académico y profesional orientado a la excelencia, la innovación y el aporte al desarrollo científico y educativo. |

|                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Datos Autor                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Nombres y apellidos                                                 | Luis Miguel Sánchez Muyulema                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Título de tercer nivel<br>(información registrada en la<br>SENECYT) | Ingeniero en Electrónica Control y Redes Industriales                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Título de cuarto nivel<br>(información registrada en la<br>SENECYT) | Magister en Sistemas de Control y Automatización Industrial                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ORCID:                                                              | <a href="https://orcid.org/0000-0001-5078-3734">https://orcid.org/0000-0001-5078-3734</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Correo electrónico                                                  | <a href="mailto:luis.sanchez@ute.edu.ec">luis.sanchez@ute.edu.ec</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Resumen hoja de vida                                                | Ingeniero en Control y Redes Industriales, con una Maestría en Sistemas de Control y Automatización Industrial. Docente de la carrera de Mecatrónica en la Universidad UTE, con una amplia experiencia en educación STEAM y robótica educativa. Ha liderado proyectos de investigación en automatización industrial y obtenido múltiples reconocimientos en competencias internacionales de robótica como RobotChallenge China 2024. Su labor está enfocada en la investigación, desarrollo tecnológico y la promoción de la robótica, contribuyendo al crecimiento de la carrera y motivando a las nuevas generaciones de ingenieros. |

## B. INTRODUCCIÓN

### Descripción

La asignatura de Electrónica Digital es de naturaleza teórico-práctica y se complementa con el uso de software especializado para el análisis y simulación de circuitos. Su propósito es proporcionar a los estudiantes los fundamentos necesarios para diseñar y construir sistemas digitales mediante el empleo de compuertas lógicas, circuitos combinacionales y circuitos secuenciales. A través de actividades prácticas y el estudio de dispositivos digitales modernos, el estudiante desarrolla la capacidad de comprender, implementar y evaluar soluciones electrónicas aplicadas a distintos contextos tecnológicos.

### Competencias

El aporte de la asignatura de Electrónica Digital al egresado de la carrera de Tecnología Superior en Electrónica se refleja en la capacidad para instalar, gestionar y brindar mantenimiento a sistemas electrónicos, de control y telecomunicaciones. Esto incluye el dominio de los principios y aplicaciones de los semiconductores, así como su integración en procesos de automatización industrial y en la transmisión y recepción de señales en sistemas de comunicación analógicos y digitales.

Además, la asignatura busca fortalecer las siguientes habilidades específicas:

- Identificar, interpretar y aplicar los principios fundamentales de la electrónica digital.

- Reconocer y analizar el comportamiento de los elementos activos y pasivos que intervienen en la construcción de circuitos.

- Utilizar adecuadamente herramientas de colaboración digital para apoyar procesos de diseño, documentación y simulación.

### Objetivos de la asignatura

La asignatura está orientada a que el estudiante desarrolle las competencias necesarias para aprender, construir, analizar y resolver problemas mediante el uso de técnicas digitales,

fortaleciendo un pensamiento analítico, crítico y creativo. En este sentido, se plantean los siguientes objetivos:

- Capacitar al estudiante, de manera teórica y experimental, en técnicas de análisis y diseño de circuitos digitales combinacionales.

- Relacionar el avance tecnológico actual con las prácticas e innovaciones presentes en la industria.

- Fomentar el análisis lógico y la capacidad de razonamiento del estudiante para la solución eficiente de problemas digitales.

- Desarrollar habilidades de pensamiento lógico y estructurado mediante la aplicación de métodos propios de la electrónica digital.

## UNIDAD 1: SISTEMAS DE NUMERACIÓN

### 1.1 Conversiones

La información que se procesa en cualquier sistema digital debe estar representada numéricamente. Para ello, es necesario utilizar un sistema de numeración que se ajuste a las características intrínsecas de este tipo de señales (Floyd, 2006).

Un sistema de numeración se define como un conjunto de símbolos capaces de representar cantidades numéricas. Asimismo, la base del sistema corresponde al número de símbolos distintos que se emplean para expresar dichas cantidades. Cada uno de estos símbolos recibe el nombre de dígito (Floyd, 2006). Los sistemas de numeración más utilizados se muestran en la Tabla 1.

**Tabla 1**

*Sistemas de numeración más utilizados*

| Sistema de numeración            | Dígitos                                                                        |

|----------------------------------|--------------------------------------------------------------------------------|

| Sistema decimal o de base 10     | Consta de diez dígitos: {0, 1, 2, 3, 4, 5, 6, 7, 8, 9}                         |

| Sistema binario o de base 2      | Consta de dos dígitos (bits): {0, 1}                                           |

| Sistema octal o de base 8        | Consta de ocho dígitos: {0, 1, 2, 3, 4, 5, 6, 7}                               |

| Sistema hexadecimal o de base 16 | Consta de diecisésis dígitos: {0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, F} |

Fuente: Floyd (2006).

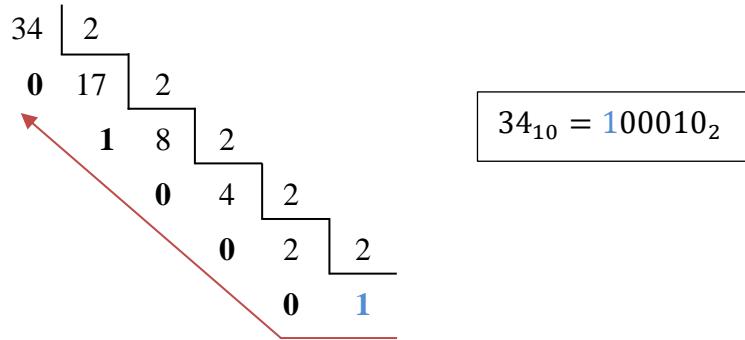

#### 1.1.1 Conversión de decimal a binario

Para convertir un número decimal a su equivalente en binario, se deben seguir los pasos descritos por Floyd (2006):

1. Realizar divisiones sucesivas entre el número decimal y la base del sistema binario (2), registrando en cada operación el cociente y el residuo. El proceso continúa hasta que el cociente final sea 0.

2. Formar el número binario tomando los residuos obtenidos en orden inverso, es decir, desde el último residuo calculado hasta el primero. Esta secuencia constituye la representación binaria del número original.

## Ejemplo

Convertir el número decimal 34 en su equivalente número binario.

## Solución

Para obtener el equivalente binario, dividimos sucesivamente entre 2 y registramos los residuos:

### 1.1.2 Conversión de binario a decimal

Para convertir un número binario a un número decimal, debemos seguir los siguientes pasos descritos por Floyd (2006):

1. Multiplicar cada bit por la potencia de 2 que le corresponde ( $2^n \dots 2^3, 2^2, 2^1, 2^0$ ), iniciando desde el bit menos significativo (derecha) hacia la izquierda.

2. Sumar todos los productos parciales obtenidos en el paso anterior. El resultado final es el valor decimal del número binario.

## Ejemplo

Convertir el número binario 1011 en su equivalente número decimal.

## Solución

Asignamos la potencia de 2 correspondiente a cada bit, desde la derecha:

|                |       |       |       |       |                                                                                                                               |

|----------------|-------|-------|-------|-------|-------------------------------------------------------------------------------------------------------------------------------|

| Potencias de 2 | $2^3$ | $2^2$ | $2^1$ | $2^0$ |                                                                                                                               |

| Número binario | 1     | 0     | 1     | 1     | $\begin{aligned} &= (1 \times 2^3) + (0 \times 2^2) + (1 \times 2^1) + (1 \times 2^0) \\ &= 8 + 0 + 2 + 1 = 11 \end{aligned}$ |

$1011_2 = 11_{10}$

### 1.1.3 Conversión de decimal a hexadecimal

Para convertir un número decimal a su equivalente en hexadecimal, se deben seguir los pasos descritos por Tocci (2011):

1. Realizar divisiones sucesivas entre el número decimal y la base del sistema hexadecimal (16), registrando el cociente y el residuo en cada operación. El proceso continúa hasta que el cociente final sea menor que 16.

2. Formar el número hexadecimal tomando los residuos y el último cociente en orden inverso, es decir, desde el último valor obtenido hasta el primero.

#### Ejemplo

Convertir el número decimal 345 en su equivalente número hexadecimal.

#### Solución

Para obtener el equivalente binario, dividimos sucesivamente entre 2 y registramos los residuos:

$$\begin{array}{r} 345 \\ \hline 16 \end{array} \quad \begin{array}{r} 9 \\ 21 \\ \hline 5 \end{array} \quad \begin{array}{r} 16 \\ 16 \\ \hline 1 \end{array}$$

$345_{10} = 159_{16}$

### 1.1.4 Conversión de hexadecimal a decimal

Para convertir un número hexadecimal a un número decimal, debemos seguir los siguientes pasos descritos por Tocci (2011):

1. Multiplicar cada dígito por la potencia de 16 que le corresponde ( $16^n \dots 16^3, 16^2, 16^1, 16^0$ ), iniciando desde el dígito menos significativo (derecha).

2. Sumar los productos parciales obtenidos en el paso anterior para obtener el número decimal final.

#### Ejemplo

Convertir el número hexadecimal 78 en su equivalente número decimal.

## Solución

Asignamos la potencia de 16 correspondiente a cada dígito:

|                 |             |             |                                                                            |

|-----------------|-------------|-------------|----------------------------------------------------------------------------|

| Potencias de 16 | $16^1$<br>↓ | $16^0$<br>↓ |                                                                            |

| Número binario  | 7           | 8           | $78_{16} = 120_{10}$ $(7 \times 16^1) + (8 \times 16^0)$ $= 112 + 8 = 120$ |

### 1.1.5 Conversión de binario a hexadecimal

Para convertir un número binario a su equivalente hexadecimal, se deben seguir los pasos descritos por Floyd (2006):

1. Agrupar los dígitos binarios de cuatro en cuatro, comenzando desde la derecha. Si el último grupo no contiene cuatro bits, se agregan ceros a la izquierda para completarlo.

2. Sustituir cada grupo de cuatro bits por su equivalente hexadecimal, según la tabla estándar de conversiones binarias.

3. Formar el número hexadecimal leyendo los dígitos resultantes de izquierda a derecha.

## Ejemplo

Convertir el número binario 01001111 en su equivalente número hexadecimal.

## Solución

|                                                                  |                        |

|------------------------------------------------------------------|------------------------|

| $0 \ 1 \ 0 \ 0 \ 1 \ 1 \ 1 \ 1$<br>_____<br>↓      ↓<br>4      F | $01001111_2 = 4F_{16}$ |

|------------------------------------------------------------------|------------------------|

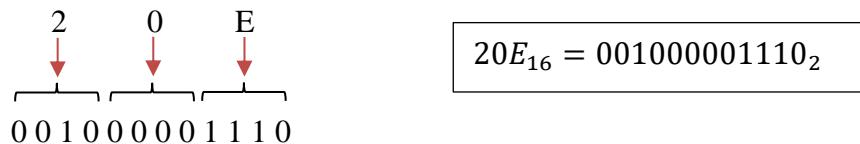

### 1.1.6 Conversión de hexadecimal a binario

Para convertir un número hexadecimal a un número binario, debemos seguir los siguientes pasos descritos por Tocci (2011):

1. Sustituir cada dígito hexadecimal por su correspondiente grupo binario de cuatro bits, utilizando la tabla estándar de equivalencias (0-F).

2. Formar el número binario concatenando los grupos obtenidos, manteniendo el orden original de los dígitos hexadecimales (de izquierda hacia la derecha).

## Ejemplo

Convertir el número hexadecimal 20E en su equivalente número binario.

## Solución

## 1.2 Aritmética Binaria

### 1.2.1 Suma Binaria

Las cuatro reglas fundamentales para sumar dígitos binarios, según Floyd (2006), son las siguientes:

- $0 + 0 = 0$  Suma 0 con acarreo 0

- $0 + 1 = 1$  Suma 1 con acarreo 0

- $1 + 0 = 1$  Suma 1 con acarreo 0

- $1 + 1 = 10$  Suma 0 con acarreo 1

Estas reglas constituyen la base de todas las operaciones de suma en sistemas digitales.

Cuando se suman números binarios de varias cifras, la última regla ( $1 + 1 = 10$ ) produce una suma parcial de 0 y un acarreo de 1 que se transfiere a la siguiente columna hacia la izquierda. Este procedimiento es equivalente al acarreo en el sistema decimal, (Tocci, 2011).

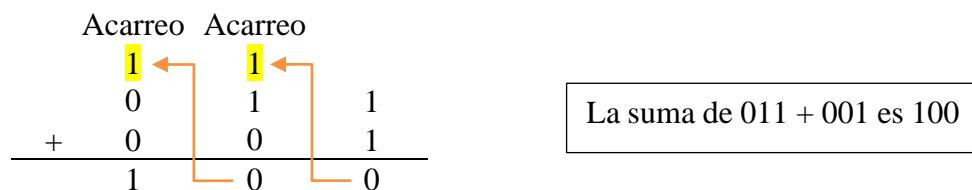

## Ejemplo

Sumar los números binarios  $011 + 001$ .

## Solución

Cuando en una suma binaria se genera un acarreo igual a 1, puede presentarse una situación en la que deban sumarse tres bits simultáneamente: un bit del primer número, un bit del segundo y el bit de acarreo proveniente de la columna anterior. En este caso, el procedimiento se realiza siguiendo las reglas establecidas por Floyd (2006).

- $1 + 0 + 0 = 01$  Suma 1 con acarreo 0

- $1 + 1 + 0 = 10$  Suma 1 con acarreo 0

- $1 + 0 + 1 = 10$  Suma 1 con acarreo 0

- $1 + 1 + 1 = 11$  Suma 1 con acarreo 1

### Ejemplo

Sumar los números binarios  $111 + 011$ .

### Solución

### 1.2.2 Resta Binaria

Las cuatro reglas fundamentales para realizar restas en sistema binario, según Floyd (2006), son:

- $0 - 0 = 0$

- $1 - 1 = 0$

- $1 - 0 = 1$

- $10 - 1 = 1$  con acarreo negativo de 1

### Ejemplo

Restar los números binarios  $11 - 10$ .

### Solución

$$\begin{array}{r} 1 & 1 \\ - 1 & 0 \\ \hline 0 & 1 \end{array}$$

La resta de  $11 - 10$  es 01

Cuando se restan números, algunas veces se genera un acarreo negativo que pasa a la siguiente columna de la izquierda. En binario, sólo se produce un acarreo negativo cuando se intenta restar 1 de 0. En este caso, cuando se acarrea un 1 a la siguiente columna de la izquierda, en la columna que se está restando se genera un 10, y entonces debe aplicarse la última de las cuatro reglas enumeradas (Floyd, 2006).

Cuando se restan números binarios, en ocasiones se genera un acarreo negativo, también llamado préstamo, que debe trasladarse a la columna inmediata de la izquierda. En el sistema binario, este préstamo ocurre únicamente cuando se intenta realizar la operación:

$$0 - 1$$

Dado que 0 no puede restarse con 1 en base 2 sin apoyo de otra columna, se toma prestado un 1 de la columna situada a la izquierda. Ese préstamo equivale a agregar 2 en términos decimales, lo cual en binario se representa como:

$$0 \rightarrow 10_2$$

Una vez convertido en  $10_2$ , puede aplicarse la última regla fundamental de la resta binaria:

$$10 - 1 = 1$$

Por lo tanto, el préstamo genera dos efectos simultáneos:

1. La columna donde ocurre la resta se transforma en  $10_2$ .

2. Se envía un acarreo negativo (préstamo) a la siguiente columna izquierda, que deberá considerarse al continuar la operación.

Este procedimiento es análogo al préstamo en el sistema decimal, pero adaptado a la base 2 (Floyd, 2006).

### Ejemplo

Restar los números binarios 101 – 011.

## Solución

Columna izquierda:

Cuando se acarrea un 1, queda 0, luego  $0 - 0 = 0$

$$\begin{array}{r} 0 \\ \times 1 \\ \hline 0 \end{array}$$

Columna central:

Acarreo negativo de 1 de la columna siguiente que da lugar a 10 en esta columna, luego  $10 - 1 = 1$

Columna derecha:

$1 - 1 = 0$

El resultado de restar  $101 - 011$  es 010.

### 1.2.3 Multiplicación Binaria

Las cuatro reglas básicas de la multiplicación de bits, según Floyd (2006) son:

- $0 \times 0 = 0$

- $0 \times 1 = 0$

- $1 \times 0 = 0$

- $1 \times 1 = 1$

La multiplicación de números binarios se realiza siguiendo el mismo procedimiento empleado en el sistema decimal. Para ello:

1. Se generan los productos parciales, multiplicando cada bit del multiplicador por cada bit del multiplicando.

2. Cada producto parcial se desplaza una posición hacia la izquierda respecto del anterior, tal como ocurre con los decimales cuando se avanza a una nueva cifra del multiplicador.

3. Finalmente, se suman todos los productos parciales, aplicando las reglas de suma binaria previamente estudiadas (Floyd, 2006).

Este método, aunque aplicado en base 2, conserva la misma estructura lógica que la multiplicación en base 10.

### Ejemplo

Multiplicar los números binarios 111 x 101.

### Solución

$$\begin{array}{r} & 1 & 1 & 1 \\ & \times & 1 & 0 & 1 \\ \hline & & 1 & 1 & 1 \\ \text{Productos} & \left. \begin{array}{c} \\ \\ \end{array} \right\} & 0 & 0 & 0 \\ & + & 1 & 1 & 1 \\ \hline & 1 & 0 & 0 & 1 & 1 \end{array}$$

La multiplicación de 111 x 101 es 100011.

### 1.2.4 División Binaria

La división binaria sigue el mismo procedimiento que la división decimal (Floyd, 2006).

### Ejemplo

Dividir los números binarios  $1100 \div 100$ .

### Solución

$$\begin{array}{r} 1 & 1 & 0 & 0 \\ 1 & 0 & 0 & \downarrow \\ \hline 0 & 1 & 0 & 0 \\ - & 1 & 0 & 0 \\ \hline 0 & 0 & 0 \end{array} \quad \begin{array}{r} 1 & 0 & 0 \\ \hline 1 & 1 \end{array}$$

La división de  $1100 \div 100$  es 11.

### 1.3 Complementos

#### 1.3.1 Complemento a 1

El complemento a 1 de un número binario se obtiene intercambiando cada bit, es decir, reemplazando los valores 1 por 0 y los valores 0 por 1 (Tocci, 2011).

### Ejemplo

Determinar el complemento a 1 del número binario 10110010.

### Solución

$$\begin{array}{cccccccc} 1 & 0 & 1 & 1 & 0 & 0 & 1 & 0 \\ \downarrow & \downarrow \\ 0 & 1 & 0 & 0 & 1 & 1 & 0 & 1 \end{array}$$

El complemento a 1 del número binario 10110010 es 01001101.

### 1.3.2 Complemento a 2

**Método I:** El complemento a 2 de un número binario se obtiene sumando 1 al bit menos significativo (LSB) del complemento a 1 (Tocci, 2011).

### Ejemplo

Determinar el complemento a 2 del número binario 10110010.

### Solución

$$\begin{array}{ccc} \text{Bit más significativo (MSB)} & & \text{Bit menos significativo (LSB)} \\ \downarrow & & \downarrow \\ \begin{array}{r} 1 & 0 & 1 & 1 & 0 & 0 & 1 & 0 \\ 0 & 1 & 0 & 0 & 1 & 1 & 0 & 1 \\ + & & & & & & 1 \\ \hline 0 & 1 & 0 & 0 & 1 & 1 & 1 & 0 \end{array} & \begin{array}{l} \text{Número binario} \\ \text{Complemento a 1} \\ \text{Sumar 1} \\ \text{Complemento a 2} \end{array} \end{array}$$

El complemento a 2 del número binario 10110010 es 01001110.

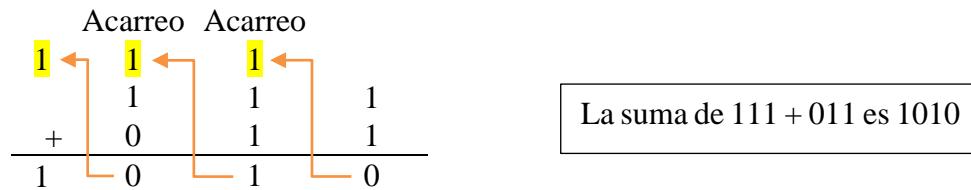

**Método II:** Un método alternativo para obtener el complemento a 2 de un número binario es el siguiente:

1. Se empieza por la derecha con el LSB y se escriben los bits como están hasta encontrar el primer 1, incluido éste.

2. Se calcula el complemento a 1 de los bits restantes (Tocci, 2011).

## Ejemplo

Determinar el complemento a 2 del mismo número binario 10110010.

## Solución

El complemento a 2 del número binario 10110010 es 01001110.

## 1.4 Códigos

### 1.4.1 Código Decimal Binario (BCD)

El código decimal binario (*BCD, Binary Coded Decimal*) es un sistema de representación en el cual cada dígito decimal se codifica de manera independiente mediante un grupo de bits binarios. Dado que el sistema BCD emplea únicamente diez combinaciones de código, la conversión entre números decimales y su representación BCD resulta sencilla y directa.

Debido a que los seres humanos leen y escriben naturalmente en el sistema decimal, el código BCD constituye una interfaz eficiente entre el mundo decimal y los sistemas digitales binarios. Ejemplos comunes de esta aplicación se encuentran en dispositivos de entrada, como los teclados, y en dispositivos de salida, como los visualizadores digitales (Tocci, 2011).

#### 1.4.1.1 Código 8421

El código 8421 es un tipo de código decimal binario (BCD) en el cual cada dígito decimal, comprendido entre 0 y 9, se representa mediante un grupo de cuatro bits binarios. La denominación 8421 hace referencia a los pesos binarios asignados a cada uno de los cuatro bits, correspondientes a  $2^3, 2^2, 2^1, 2^0$ , respectivamente.

La principal ventaja del código 8421 radica en la facilidad de conversión entre los números decimales y su representación binaria, lo que lo convierte en un método ampliamente utilizado en sistemas digitales que interactúan directamente con datos introducidos o visualizados por el

usuario (Tocci, 2011). Las diez combinaciones binarias que representan los dígitos decimales del 0 al 9 se presentan en la Tabla 2.

**Tabla 2**

*Conversión decimal / BCD*

| Decimal | Binario |

|---------|---------|

| 0       | 0000    |

| 1       | 0001    |

| 2       | 0010    |

| 3       | 0011    |

| 4       | 0100    |

| 5       | 0101    |

| 6       | 0110    |

| 7       | 0111    |

| 8       | 1000    |

| 9       | 1001    |

**Fuente:** Tocci (2011).

El código 8421 es el tipo de código BCD más ampliamente utilizado. Por esta razón, cuando se hace referencia de manera general al código BCD, se entiende que se trata del código 8421, salvo que se indique explícitamente otro tipo de codificación (Tocci, 2011).

**Nota:** Es importante señalar que, al emplear cuatro bits, es posible representar dieciséis combinaciones binarias, comprendidas entre 0000 y 1111. Sin embargo, en el código BCD 8421 solo se utilizan diez de estas combinaciones, correspondientes a los dígitos decimales del 0 al 9. Las seis combinaciones restantes (1010, 1011, 1100, 1101, 1110 y 1111) no son válidas dentro de este sistema de codificación (Tocci, 2011).

### ***Conversión decimal a BCD***

La conversión de un número decimal a su representación en código decimal binario (BCD) se realiza reemplazando cada dígito decimal por su correspondiente código binario de cuatro bits (Carpinelli, 2023).

### **Ejemplo**

Convertir el número decimal 98 a un número en código BCD.

### Solución

1 0 0 1      1 0 0 0

9                8

En código BCD el número es 10011000.

### Conversión BCD a decimal

El procedimiento inicia desde la derecha, comenzando por el bit menos significativo (LSB), y consiste en dividir el código binario en grupos de cuatro bits. Luego, se determina el dígito decimal correspondiente a cada grupo, leyendo los resultados de derecha a izquierda (Carpinelli, 2023).

### Ejemplo

Convertir el número en código BCD 001101010001 a un número decimal.

### Solución

0 0 1 1      0 1 0 1      0 0 0 1

3                5                1

En decimal el número es 351.

## 1.4.2 Códigos Decimales

### 1.4.2.1 Código Gray

El código Gray es un código no ponderado y no aritmético, es decir, no posee pesos específicos asignados a las posiciones de sus bits. Su característica más relevante es que entre dos códigos consecutivos solo cambia un bit, lo que reduce significativamente la posibilidad de errores durante las transiciones entre valores adyacentes. Esta propiedad resulta especialmente útil en aplicaciones como los codificadores de posición angular, donde la probabilidad de error aumenta conforme se incrementa el número de cambios simultáneos de bits entre estados consecutivos (Tocci, 2011).

La Tabla 3 presenta el código Gray de cuatro bits correspondiente a los números decimales del 0 al 15. Como referencia, se incluyen también las representaciones binarias equivalentes. Al igual que el sistema binario, el código Gray puede definirse con cualquier número de bits; sin embargo, en este caso particular, se garantiza que entre dos valores sucesivos solo se modifica un único bit, manteniéndose los demás sin cambio. En el código Gray de cuatro bits mostrado, el bit que varía entre valores consecutivos corresponde al tercer bit contado desde la derecha, mientras que los demás permanecen constantes (Tocci, 2011).

**Tabla 3**

*Código Gray de cuatro bits*

| Decimal | Binario | Gray |

|---------|---------|------|

| 0       | 0000    | 0000 |

| 1       | 0001    | 0001 |

| 2       | 0010    | 0011 |

| 3       | 0011    | 0010 |

| 4       | 0100    | 0110 |

| 5       | 0101    | 0111 |

| 6       | 0110    | 0101 |

| 7       | 0111    | 0100 |

| 8       | 1000    | 1100 |

| 9       | 1001    | 1101 |

| 10      | 1010    | 1111 |

| 11      | 1011    | 1110 |

| 12      | 1100    | 1010 |

| 13      | 1101    | 1011 |

| 14      | 1110    | 1001 |

| 15      | 1111    | 1000 |

**Fuente:** Tocci (2011).

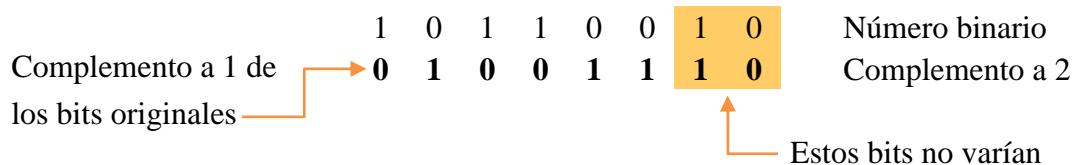

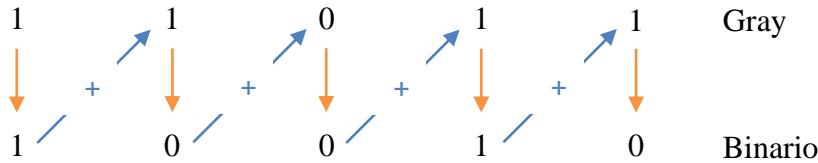

### **Conversión binario a Gray**

El bit más significativo (Most Significant Bit, MSB) del código Gray es idéntico al MSB del número binario correspondiente. A partir de este bit y avanzando de izquierda a derecha, cada bit subsiguiente del código Gray se obtiene sumando módulo 2 (operación XOR) cada par de bits adyacentes del número binario. En este proceso, los acarreos se descartan, ya que la operación se realiza sin consideración de transporte (Tocci, 2011).

### Ejemplo

Convertir el número binario 10110 a un número en código Gray.

### Solución

En código Gray el número es 11101.

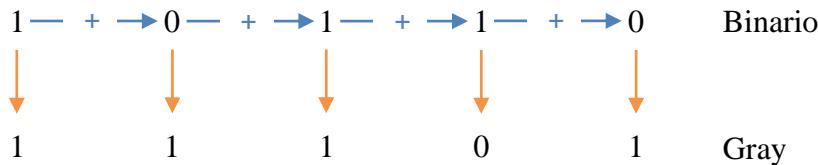

### Conversión Gray a binario

El bit más significativo (bit más a la izquierda) en el código binario es el mismo que el correspondiente bit en código Gray. A cada bit del código binario generado se le suma el bit en código Gray de la siguiente posición adyacente. Los acarreos se descartan (Tocci, 2011).

### Ejemplo

Convertir el número en código Gray 11011 a un número binario.

### Solución

En binario el número es 10010.

### 1.4.2.2 Códigos alfanuméricicos

Para la comunicación digital no solo se requieren números, sino también letras, símbolos y caracteres de control. Los códigos alfanuméricicos permiten representar dígitos decimales y caracteres alfábéticos, así como otros símbolos e instrucciones necesarios para la transmisión y el procesamiento de la información (Carpinelli, 2023).

Un código alfanumérico básico debe representar al menos los diez dígitos decimales y las 26 letras del alfabeto, lo que corresponde a 36 símbolos distintos. Esta cantidad requiere un mínimo de seis bits, ya que cinco bits solo permiten 32 combinaciones posibles. Con seis bits se obtienen 64 combinaciones, lo que posibilita incluir, además de números y letras, símbolos adicionales y caracteres de control. El código ASCII es el sistema alfanumérico más ampliamente utilizado en los sistemas digitales (Floyd, 2006).

#### 1.4.2.2.1 Código ASCII

El American Standard Code for Information Interchange (ASCII, código estándar americano para el intercambio de información) es un código alfanumérico universalmente aceptado, que se utiliza en la mayoría de las computadoras y otros equipos electrónicos. La mayor parte de los teclados de computadora se encuentran estandarizados de acuerdo con el código ASCII y, cuando se pulsa una letra, un número o un comando de control, es el código ASCII el que se introduce en la computadora (Tocci, 2011).

El código ASCII dispone de 128 caracteres, los cuales se representan mediante un código binario de 7 bits. No obstante, el código ASCII puede considerarse como un código de 8 bits, en el que el bit más significativo (MSB) siempre es 0. En notación hexadecimal, este código de 8 bits abarca los valores comprendidos entre 00 y 7F. Los primeros 32 caracteres ASCII corresponden a caracteres de control no gráficos, los cuales no se imprimen ni se presentan en pantalla y se utilizan exclusivamente para propósitos de control. Ejemplos de estos caracteres son nulo, avance de línea, inicio de texto y escape. Los demás caracteres son símbolos gráficos que pueden imprimirse o mostrarse en pantalla, e incluyen las letras del alfabeto en mayúsculas y minúsculas, los diez dígitos decimales, los signos de puntuación y otros símbolos comúnmente utilizados (Tocci, 2011).

La Figura 1 presenta un listado del código ASCII, junto con su representación decimal, hexadecimal y binaria para cada carácter y símbolo. En la primera columna se enumeran los nombres de los 32 caracteres de control, codificados en hexadecimal desde 00 hasta 1F, y en las columnas restantes se muestran los símbolos gráficos, representados en hexadecimal desde 20 hasta 7F (Floyd, 2006).

| Símbolos gráficos |         |     |         |     |        |     |         |     |         |     |         |     |  |

|-------------------|---------|-----|---------|-----|--------|-----|---------|-----|---------|-----|---------|-----|--|

| Hex               | Símbolo | Dec | Binario | Hex | Nombre | Dec | Binario | Hex | Símbolo | Dec | Binario | Hex |  |

| 00                | space   | 32  | 0100000 | 20  | @      | 64  | 1000000 | 40  | `       | 96  | 1100000 | 60  |  |

| 01                | !       | 33  | 0100001 | 21  | A      | 65  | 1000001 | 41  | a       | 97  | 1100001 | 61  |  |

| 02                | "       | 34  | 0100010 | 22  | B      | 66  | 1000010 | 42  | b       | 98  | 1100010 | 62  |  |

| 03                | #       | 35  | 0100011 | 23  | C      | 67  | 1000011 | 43  | c       | 99  | 1100011 | 63  |  |

| 04                | \$      | 36  | 0100100 | 24  | D      | 68  | 1000100 | 44  | d       | 100 | 1100100 | 64  |  |

| 05                | %       | 37  | 0100101 | 25  | E      | 69  | 1000101 | 45  | e       | 101 | 1100101 | 65  |  |

| 06                | &       | 38  | 0100110 | 26  | F      | 70  | 1000110 | 46  | f       | 102 | 1100110 | 66  |  |

| 07                | '       | 39  | 0100111 | 27  | G      | 71  | 1000111 | 47  | g       | 103 | 1100111 | 67  |  |

| 08                | (       | 40  | 0101000 | 28  | H      | 72  | 1001000 | 48  | h       | 104 | 1101000 | 68  |  |

| 09                | )       | 41  | 0101001 | 29  | I      | 73  | 1001001 | 49  | i       | 105 | 1101001 | 69  |  |

| 0A                | *       | 42  | 0101010 | 2A  | J      | 74  | 1001010 | 4A  | j       | 106 | 1101010 | 6A  |  |

| 0B                | +       | 43  | 0101011 | 2B  | K      | 75  | 1001011 | 4B  | k       | 107 | 1101011 | 6B  |  |

| 0C                | ,       | 44  | 0101100 | 2C  | L      | 76  | 1001100 | 4C  | l       | 108 | 1101100 | 6C  |  |

| 0D                | -       | 45  | 0101101 | 2D  | M      | 77  | 1001101 | 4D  | m       | 109 | 1101101 | 6D  |  |

| 0E                | .       | 46  | 0101110 | 2E  | N      | 78  | 1001110 | 4E  | n       | 110 | 1101110 | 6E  |  |

| 0F                | /       | 47  | 0101111 | 2F  | O      | 79  | 1001111 | 4F  | o       | 111 | 1101111 | 6F  |  |

| 10                | 0       | 48  | 0110000 | 30  | P      | 80  | 1010000 | 50  | p       | 112 | 1110000 | 70  |  |

| 11                | 1       | 49  | 0110001 | 31  | Q      | 81  | 1010001 | 51  | q       | 113 | 1110001 | 71  |  |

| 12                | 2       | 50  | 0110010 | 32  | R      | 82  | 1010010 | 52  | r       | 114 | 1110010 | 72  |  |

| 13                | 3       | 51  | 0110011 | 33  | S      | 83  | 1010011 | 53  | s       | 115 | 1110011 | 73  |  |

| 14                | 4       | 52  | 0110100 | 34  | T      | 84  | 1010100 | 54  | t       | 116 | 1110100 | 74  |  |

| 15                | 5       | 53  | 0110101 | 35  | U      | 85  | 1010101 | 55  | u       | 117 | 1110101 | 75  |  |

| 16                | 6       | 54  | 0110110 | 36  | V      | 86  | 1010110 | 56  | v       | 118 | 1110110 | 76  |  |

| 17                | 7       | 55  | 0110111 | 37  | W      | 87  | 1010111 | 57  | w       | 119 | 1110111 | 77  |  |

| 18                | 8       | 56  | 0111000 | 38  | X      | 88  | 1011000 | 58  | x       | 120 | 1111000 | 78  |  |

| 19                | 9       | 57  | 0111001 | 39  | Y      | 89  | 1011001 | 59  | y       | 121 | 1111001 | 79  |  |

| 1A                | :       | 58  | 0111010 | 3A  | Z      | 90  | 1011010 | 5A  | z       | 122 | 1111010 | 7A  |  |

| 1B                | ;       | 59  | 0111011 | 3B  | [      | 91  | 1011011 | 5B  | {       | 123 | 1111011 | 7B  |  |

| 1C                | <       | 60  | 0111100 | 3C  | \      | 92  | 1011100 | 5C  |         | 124 | 1111100 | 7C  |  |

| 1D                | =       | 61  | 0111101 | 3D  | ]      | 93  | 1011101 | 5D  | }       | 125 | 1111101 | 7D  |  |

| 1E                | >       | 62  | 0111110 | 3E  | ^      | 94  | 1011110 | 5E  | ~       | 126 | 1111110 | 7E  |  |

| 1F                | ?       | 63  | 0111111 | 3F  | _      | 95  | 1011111 | 5F  | Del     | 127 | 1111111 | 7F  |  |

**Figura 1** Código ASCII (American Standard Code for Information Interchange).

Fuente: Floyd (2006).

| Nombre | Decimal | Hex | Tecla  | Descripción                   |

|--------|---------|-----|--------|-------------------------------|

| NUL    | 0       | 00  | CTRL @ | Carácter nulo                 |

| SOH    | 1       | 01  | CTRL A | Inicio de cabecera            |

| STX    | 2       | 02  | CTRL B | Inicio de texto               |

| ETX    | 3       | 03  | CTRL C | Fin de texto                  |

| EOT    | 4       | 04  | CTRL D | Fin de transmisión            |

| ENQ    | 5       | 05  | CTRL E | Petición                      |

| ACK    | 6       | 06  | CTRL F | Reconocimiento                |

| BEL    | 7       | 07  | CTRL G | Timbre                        |

| BS     | 8       | 08  | CTRL H | Barra espaciadora             |

| HT     | 9       | 09  | CTRL I | Tabulador horizontal          |

| LF     | 10      | 0A  | CTRL J | Avance de línea               |

| VT     | 11      | 0B  | CTRL K | Tabulador vertical            |

| FF     | 12      | 0C  | CTRL L | Salto de página               |

| CR     | 13      | 0D  | CTRL M | Retorno de carro              |

| SO     | 14      | 0E  | CTRL N | Desplazamiento de salida      |

| SI     | 15      | 0F  | CTRL O | Desplazamiento de entrada     |

| DLE    | 16      | 10  | CTRL P | Escape de enlace de datos     |

| DC1    | 17      | 11  | CTRL Q | Dispositivo de control 1      |

| DC2    | 18      | 12  | CTRL R | Dispositivo de control 2      |

| DC3    | 19      | 13  | CTRL S | Dispositivo de control 3      |

| DC4    | 20      | 14  | CTRL T | Dispositivo de control 4      |

| NAK    | 21      | 15  | CTRL U | Confirmación negativa         |

| SYN    | 22      | 16  | CTRL V | Sincronismo                   |

| ETB    | 23      | 17  | CTRL W | Fin del bloque de transmisión |

| CAN    | 24      | 18  | CTRL X | Cancelación                   |

| EM     | 25      | 19  | CTRL Y | Fin del dispositivo           |

| SUB    | 26      | 1A  | CTRL Z | Sustitución                   |

| ESC    | 27      | 1B  | CTRL [ | Escape                        |

| FS     | 28      | 1C  | CTRL / | Separador de archivo          |

| GS     | 29      | 1D  | CTRL ] | Separador de grupo            |

| RS     | 30      | 1E  | CTRL ^ | Separador de registro         |

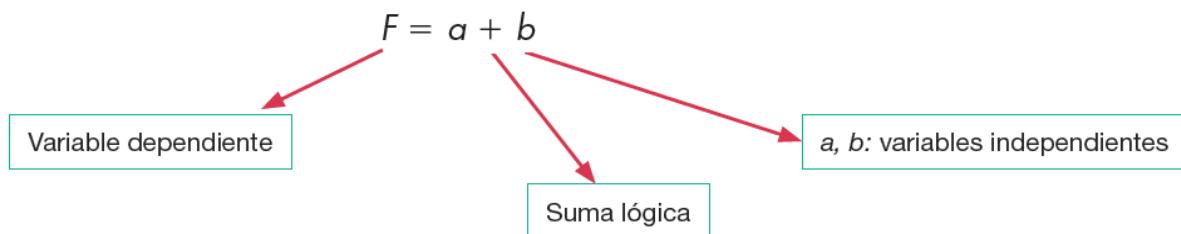

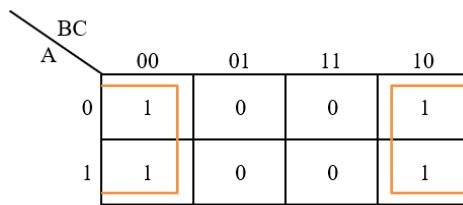

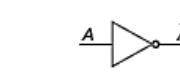

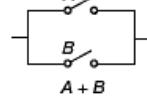

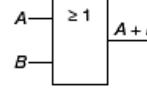

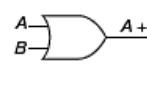

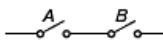

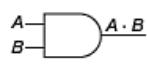

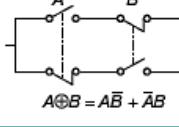

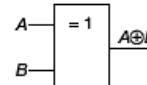

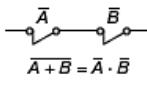

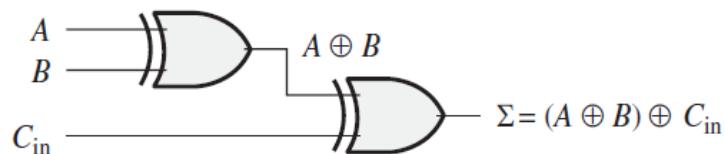

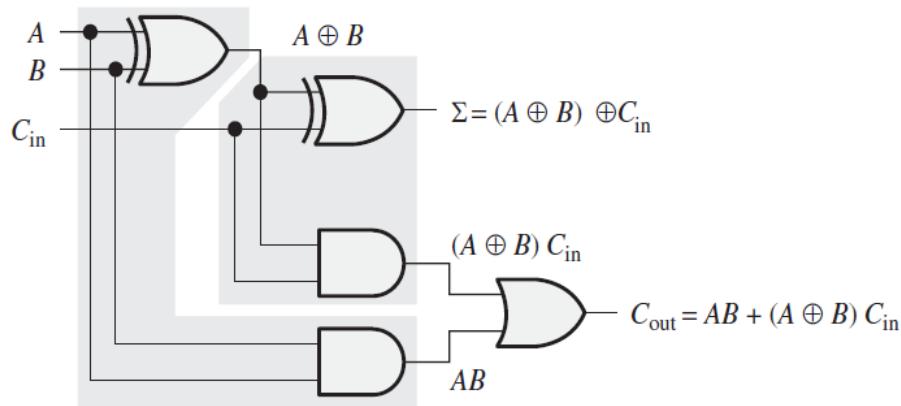

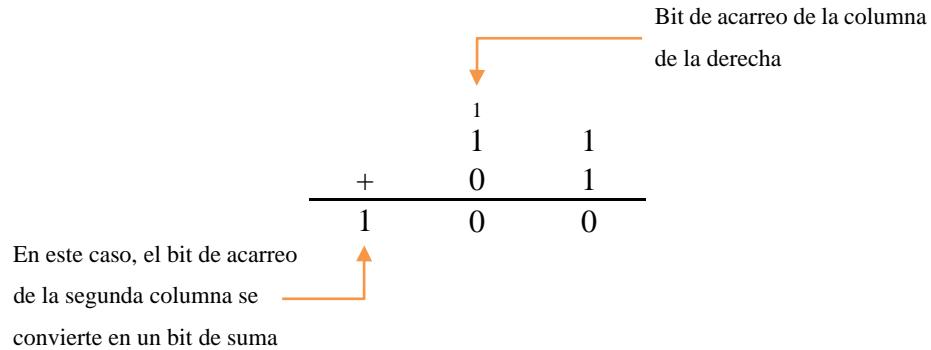

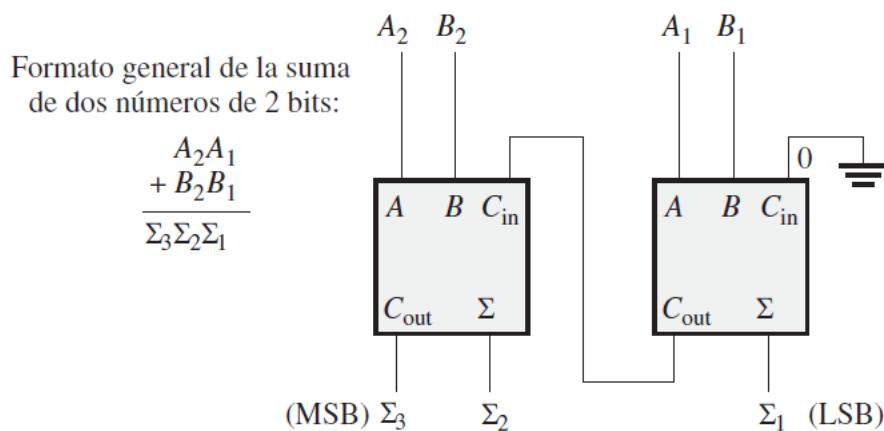

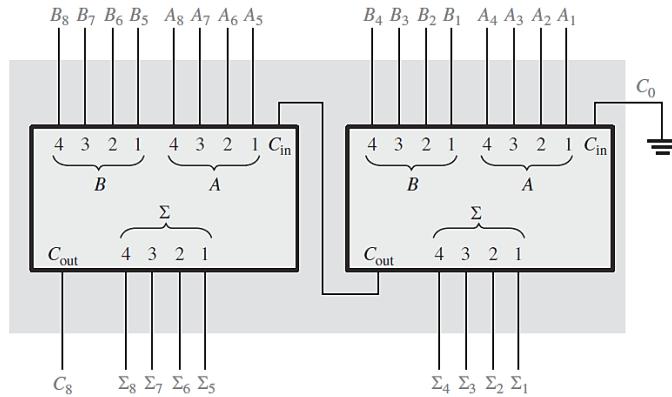

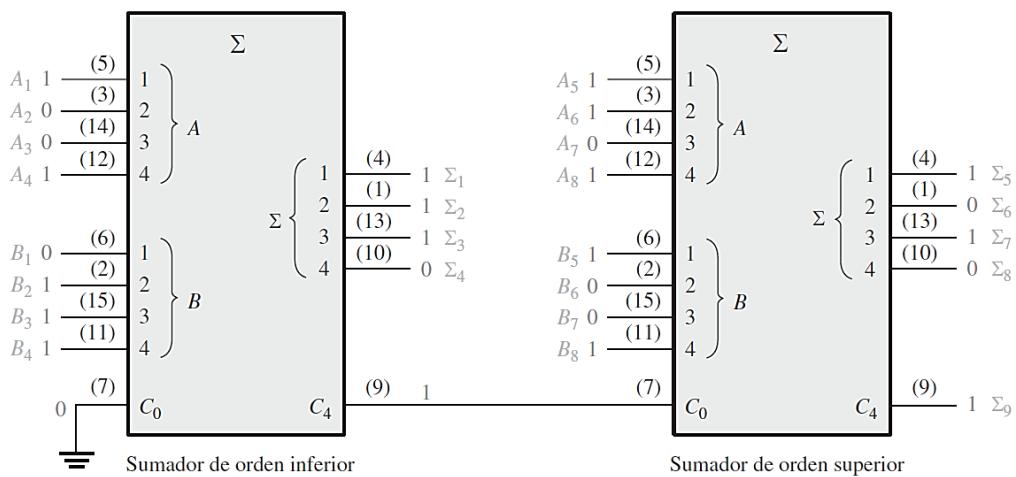

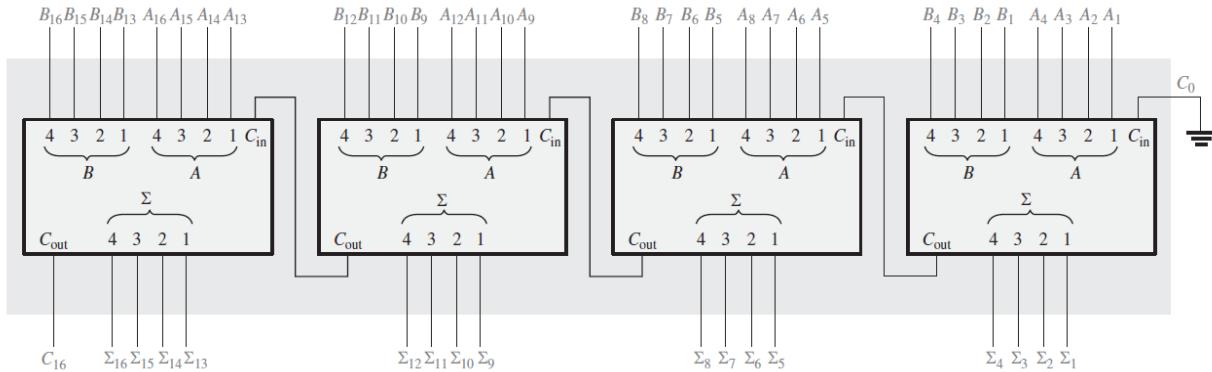

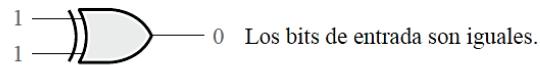

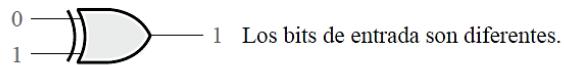

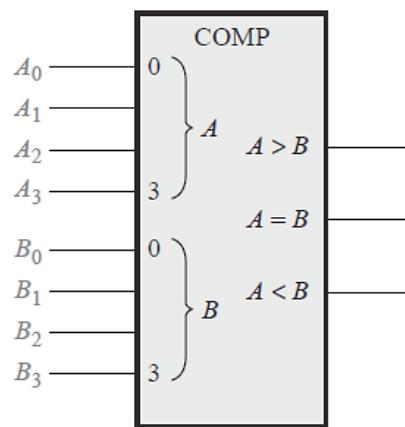

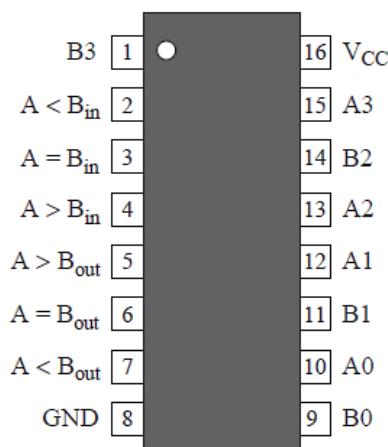

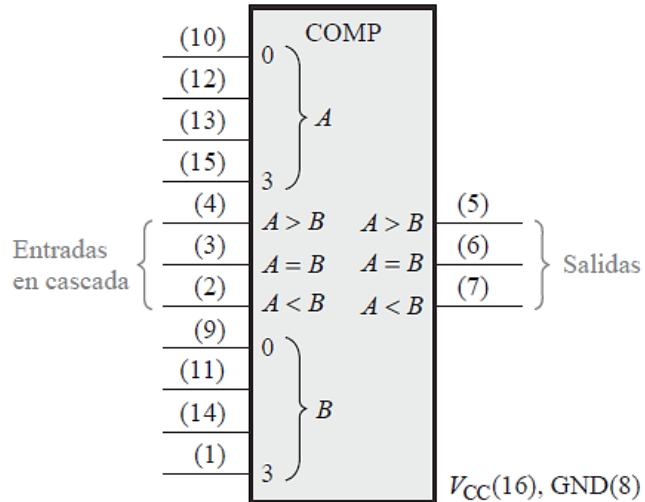

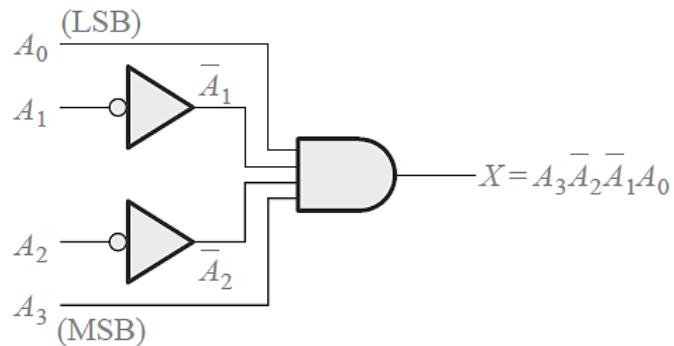

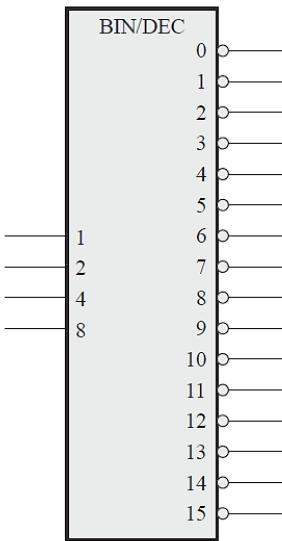

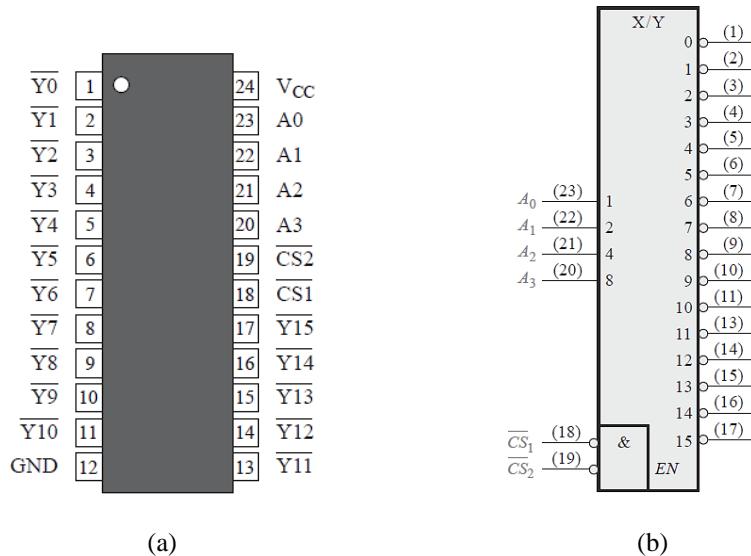

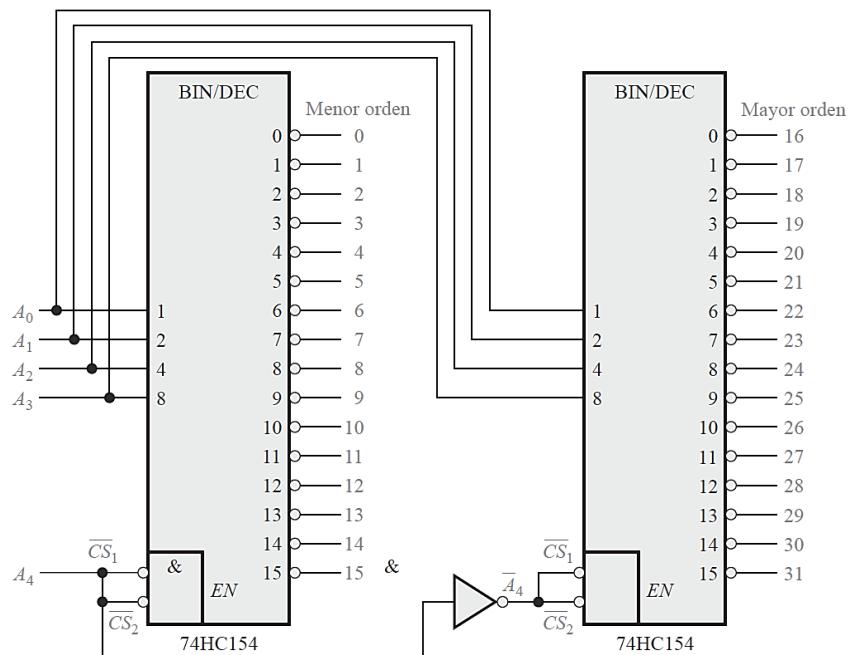

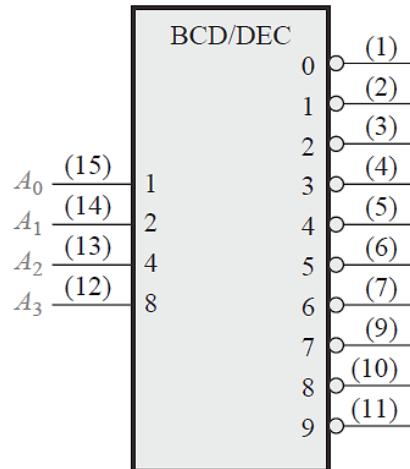

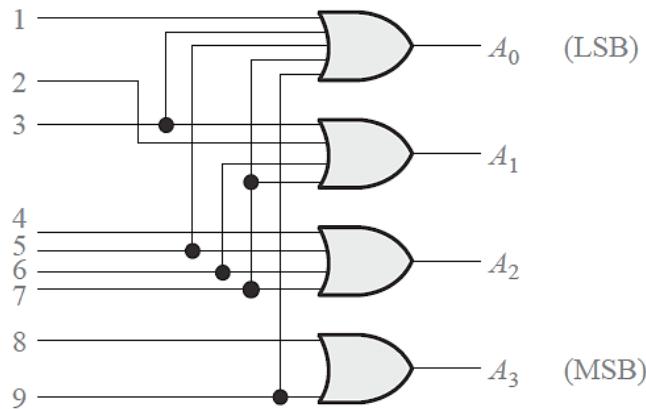

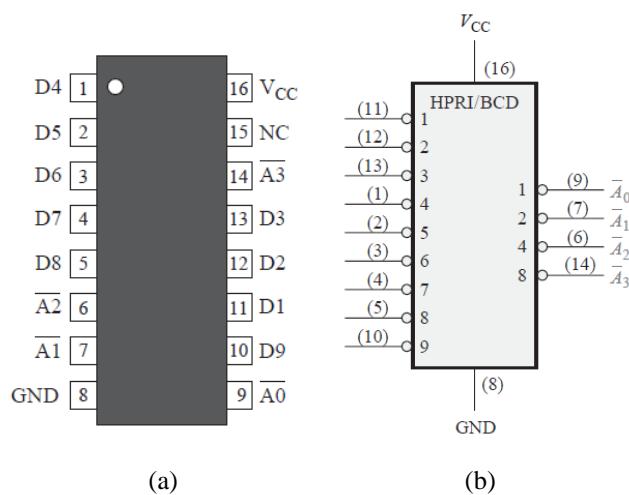

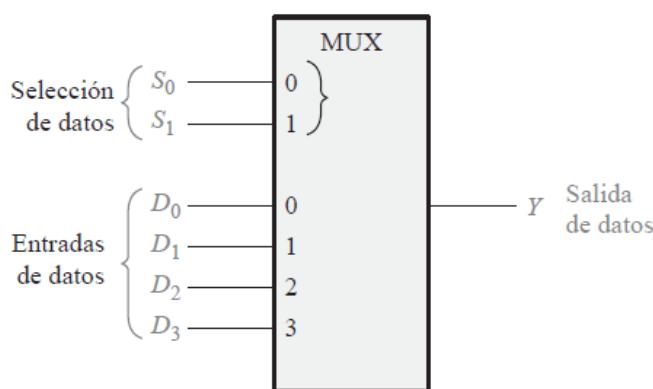

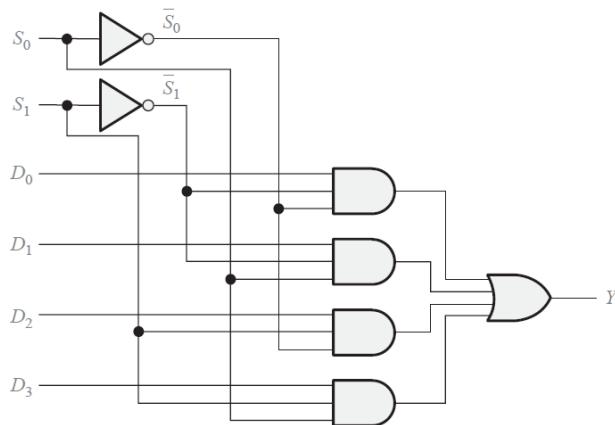

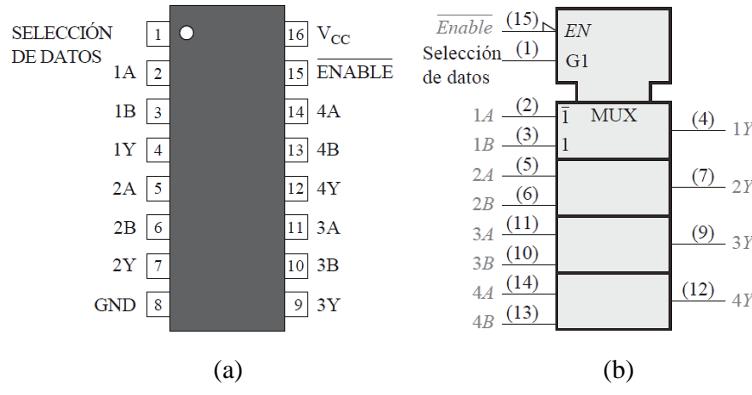

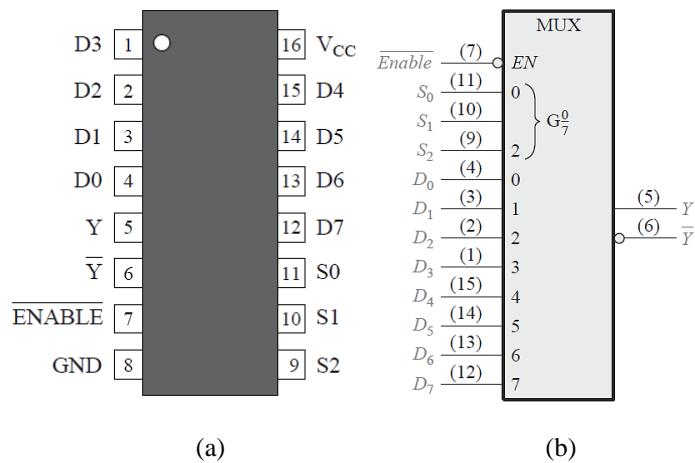

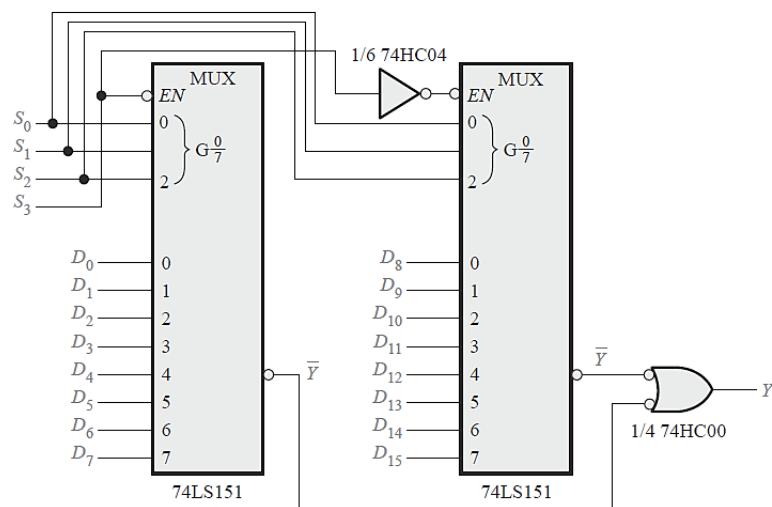

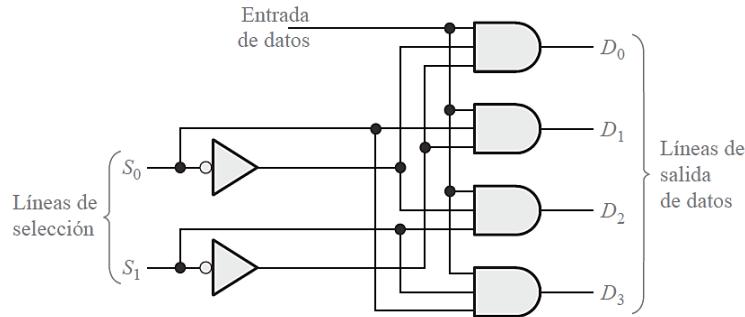

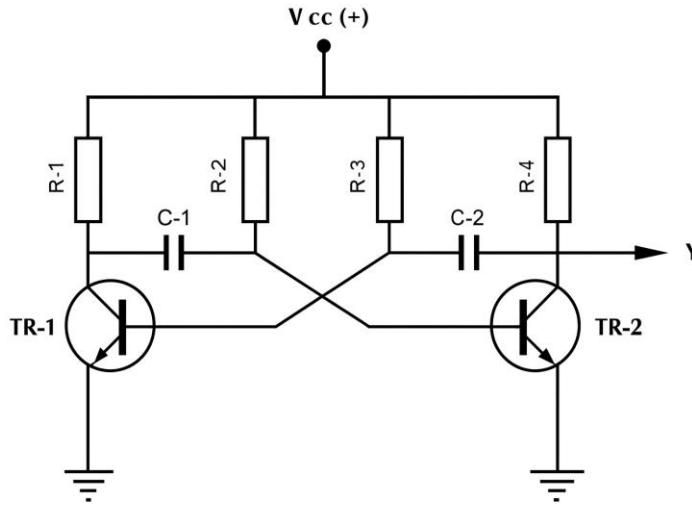

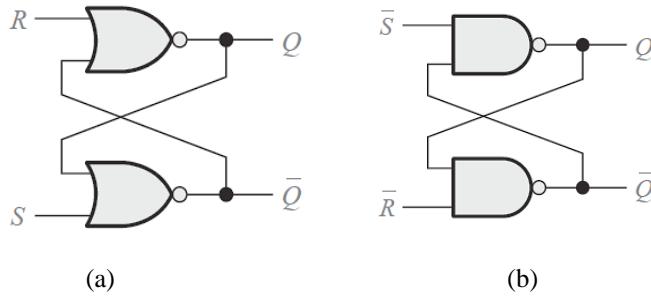

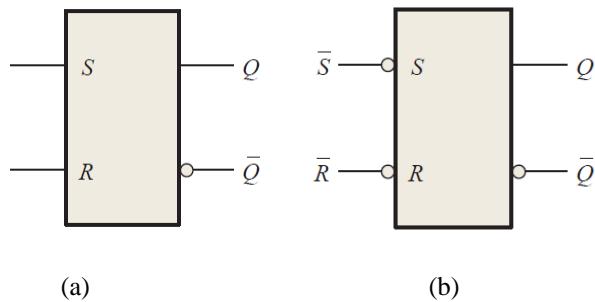

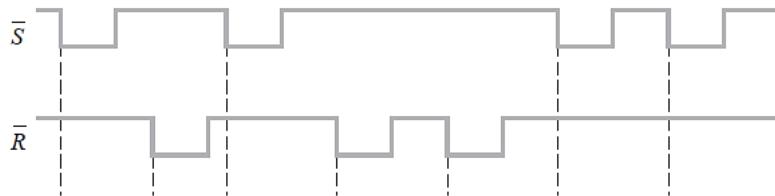

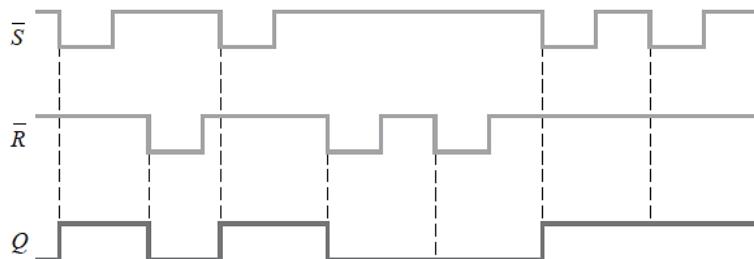

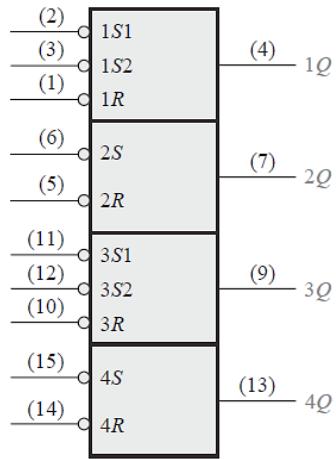

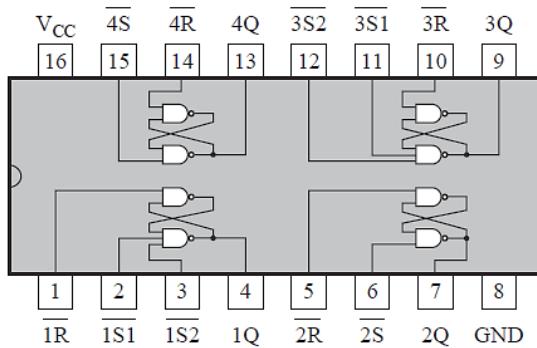

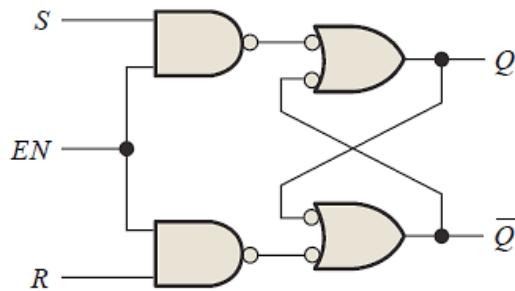

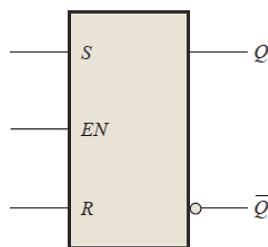

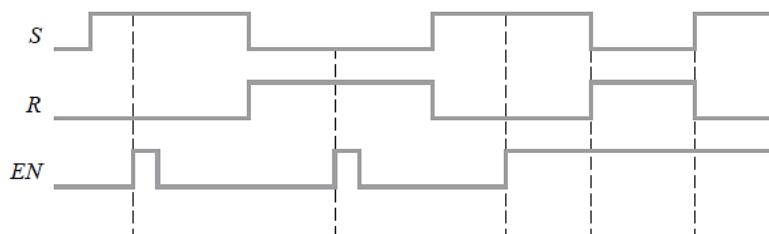

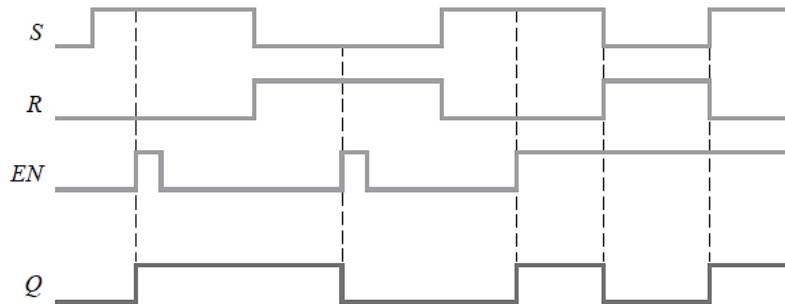

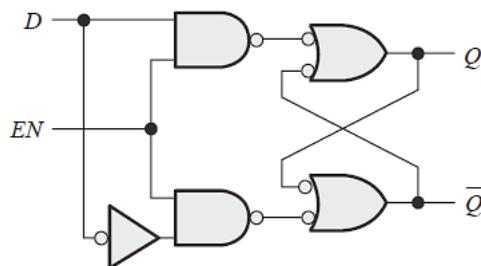

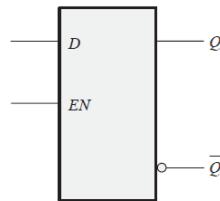

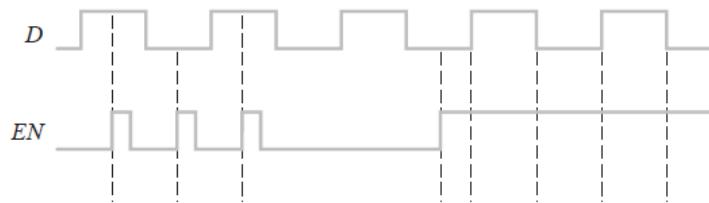

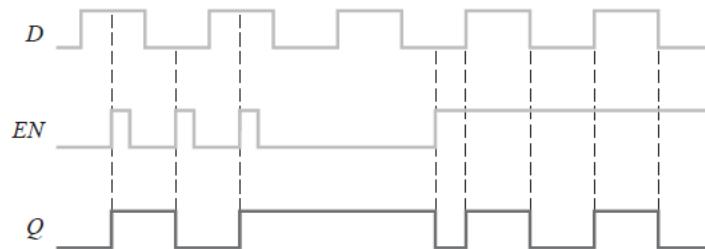

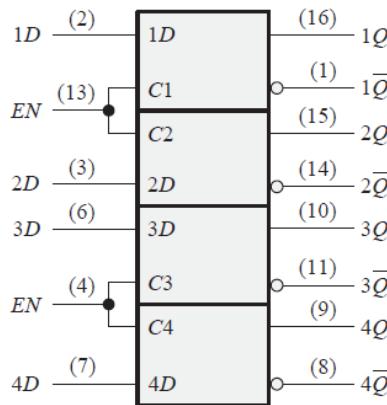

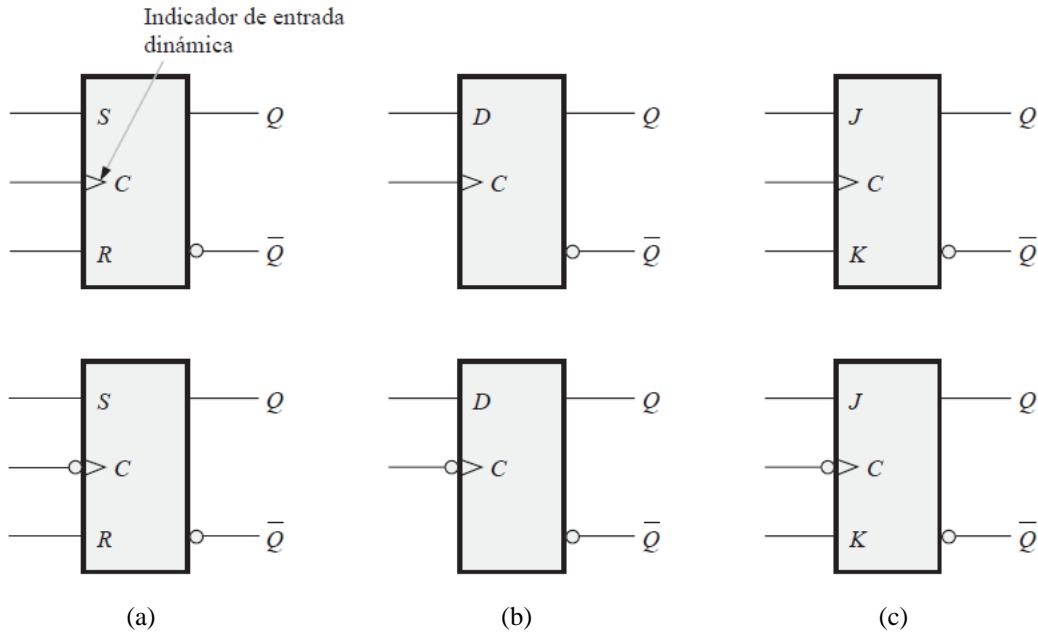

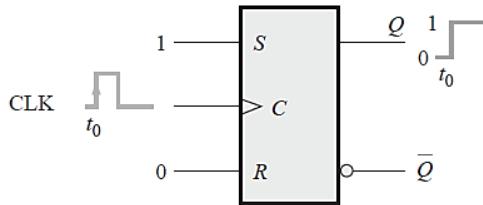

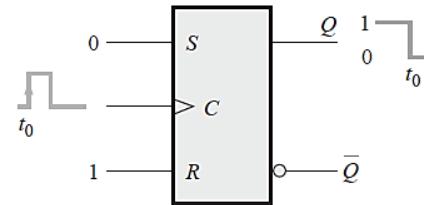

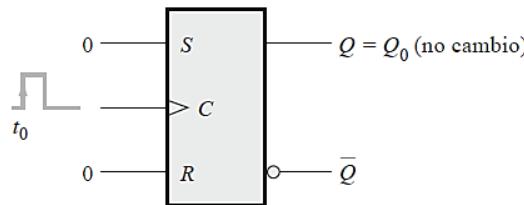

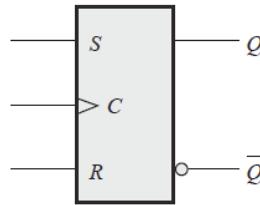

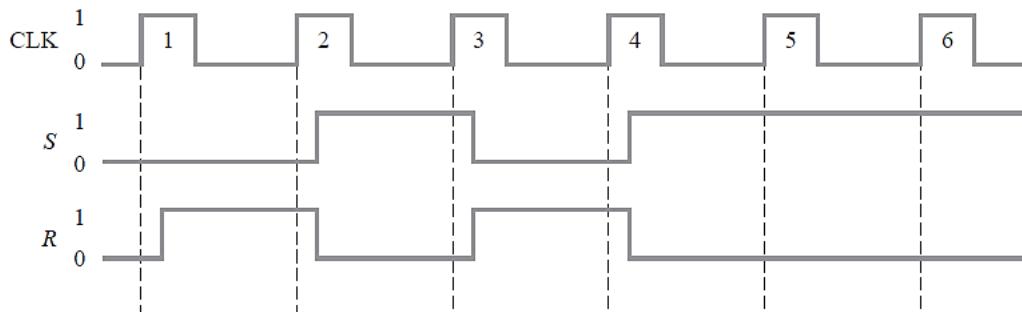

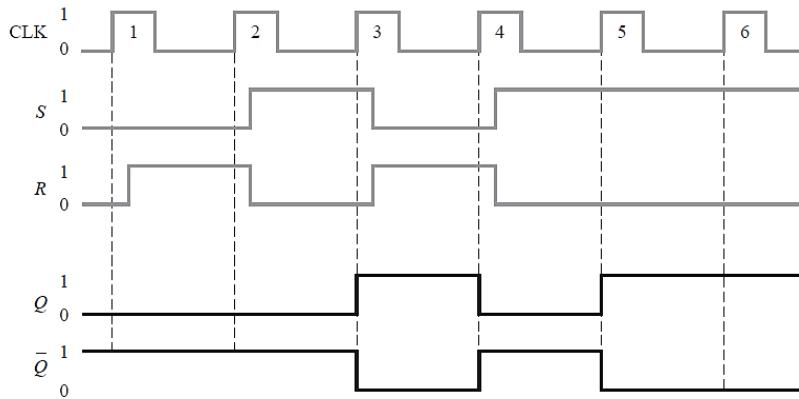

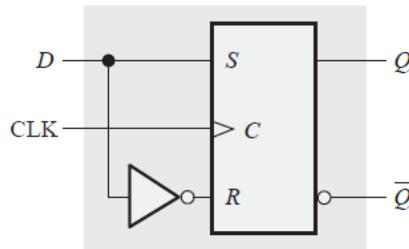

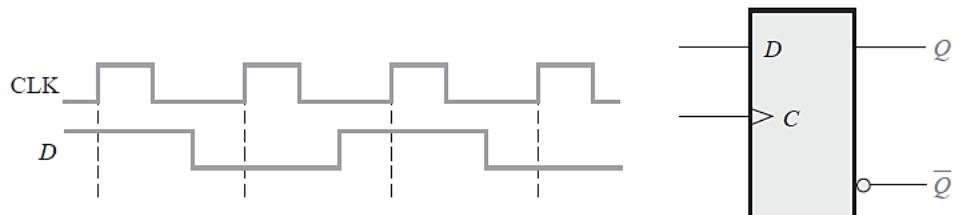

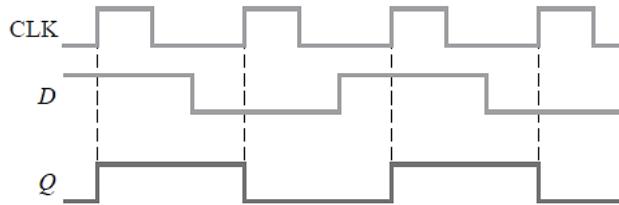

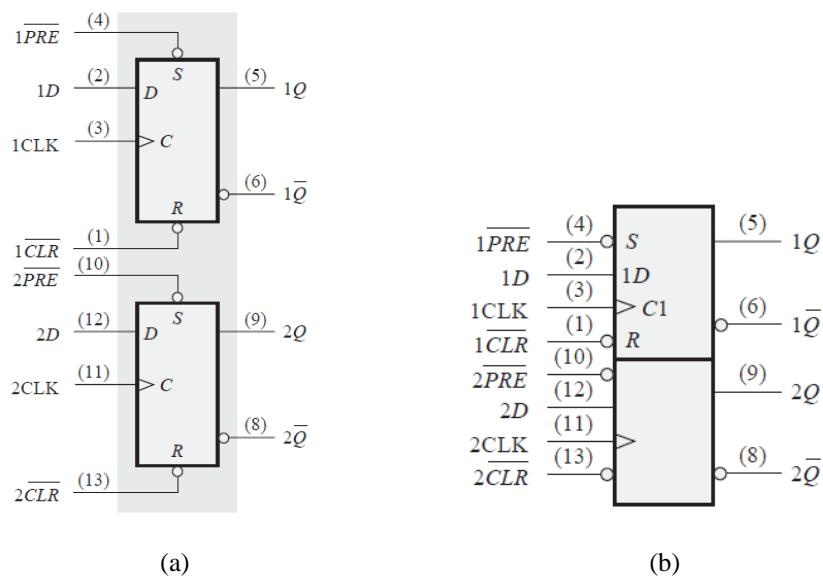

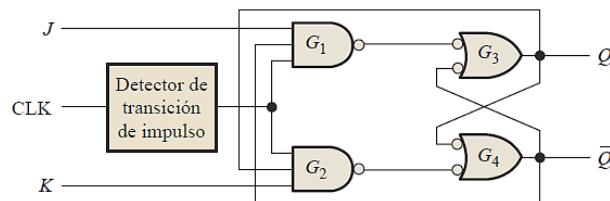

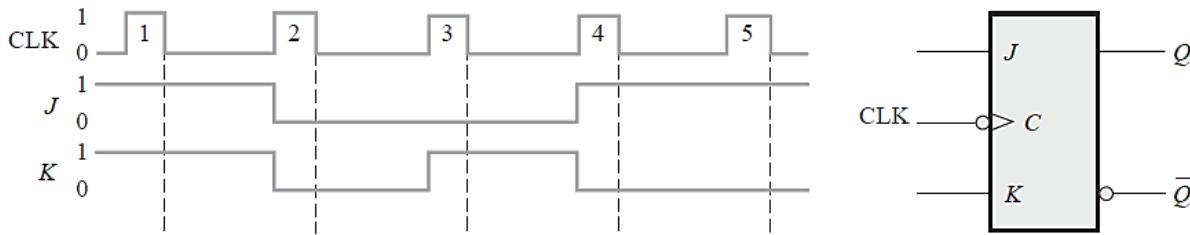

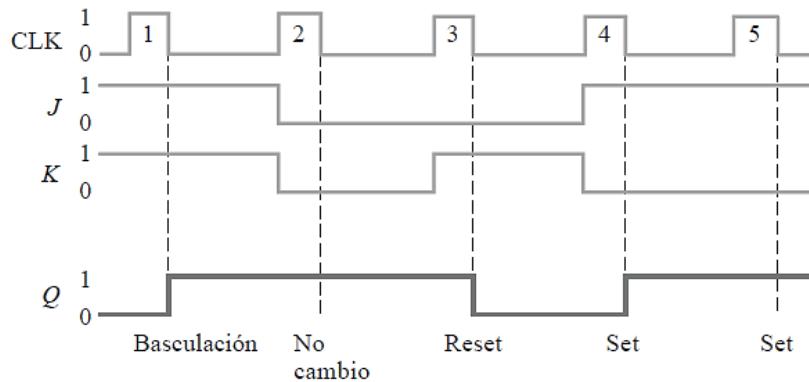

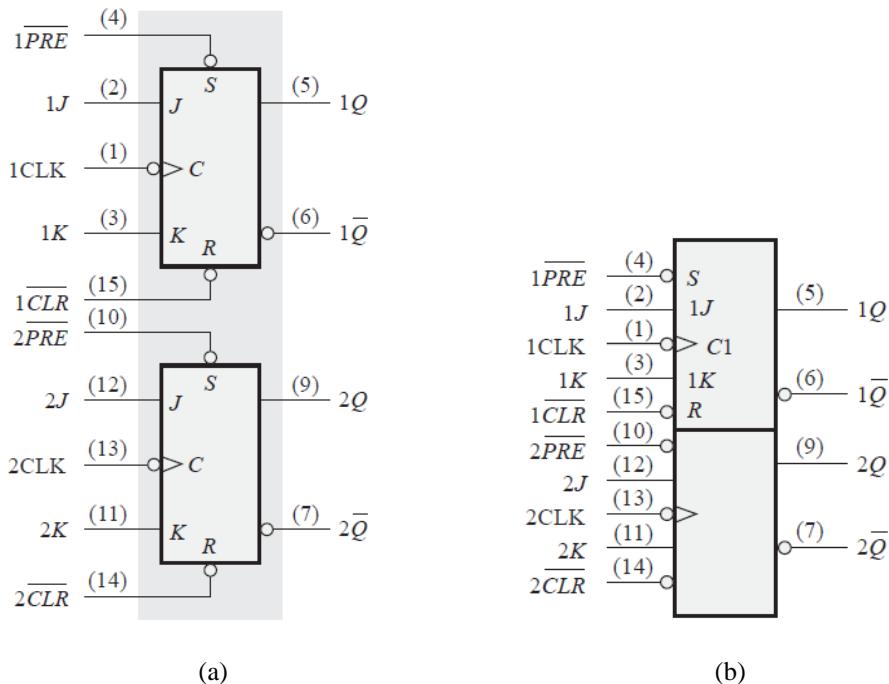

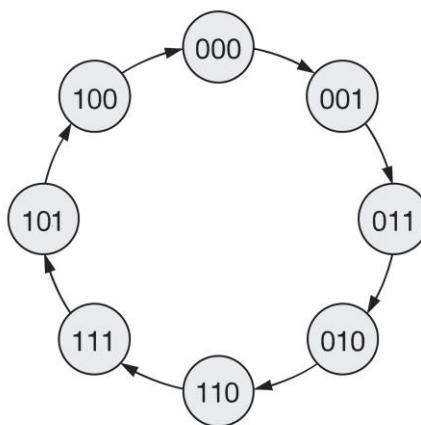

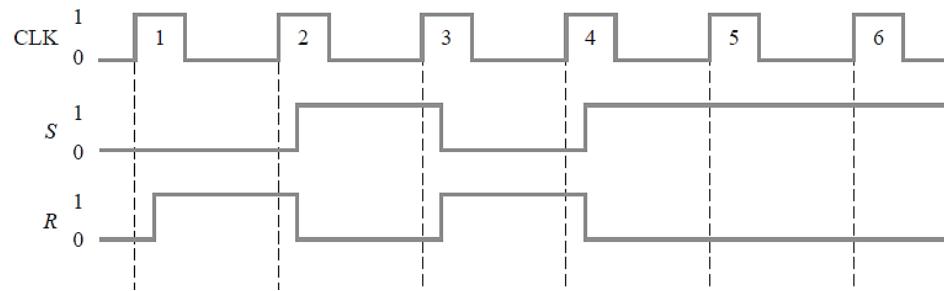

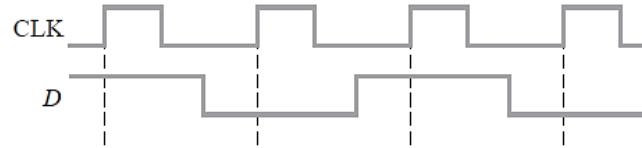

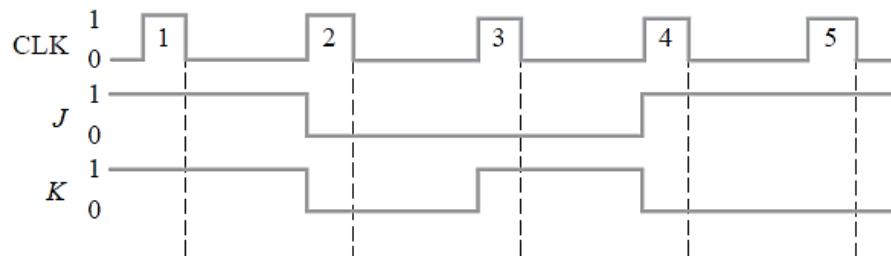

| US     | 31      | 1F  | CTRL _ | Separador de unidad           |